# CSIR-NET, GATE, SET, JEST, IIT-JAM, BARC, TIFR

Contact: 8830156303 | 8329503213

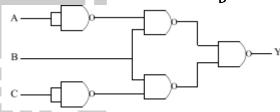

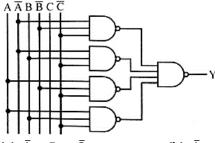

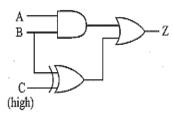

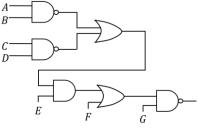

# **Physical Science**

# **ELECTRONICS**

Previous Year Questions [Topic-Wise]

With Answer Key

CSIR-NET/JRF, GATE, JEST, TIFR

| NO  | TOPIC                                   | PAGE NO: |  |  |  |  |

|-----|-----------------------------------------|----------|--|--|--|--|

|     | ANOLOG ELECTRONICS                      |          |  |  |  |  |

| 1.  | <u>OP-AMP</u>                           | 1        |  |  |  |  |

| 2.  | Network Theory & Circuit Analysis       | 19       |  |  |  |  |

| 3.  | <u>Diodes</u>                           | 25       |  |  |  |  |

| 4.  | Bipolar Junction Transistor             | 32       |  |  |  |  |

| 5.  | MOSFET, JFET                            | 40       |  |  |  |  |

| 6.  | Semiconductor                           | 42       |  |  |  |  |

| 7.  | Transient Circuit                       | 45       |  |  |  |  |

| 8.  | ADC & DAC                               | 49       |  |  |  |  |

| 9.  | Experimental Instruments Based Problems | 51       |  |  |  |  |

| 10. | Wave Shaping                            | 55       |  |  |  |  |

| 11. | Frequency Modulation                    | 60       |  |  |  |  |

| 12. | <u>Oscillatory</u>                      | 61       |  |  |  |  |

|     | DIGITAL ELECTRONICS                     |          |  |  |  |  |

| 1.  | Boolean Algebra                         | 62       |  |  |  |  |

| 2.  | Logic Gates                             | 65       |  |  |  |  |

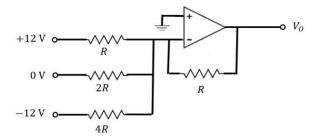

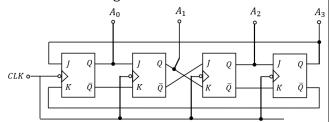

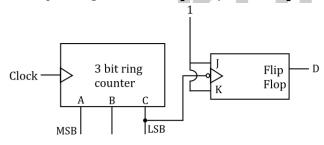

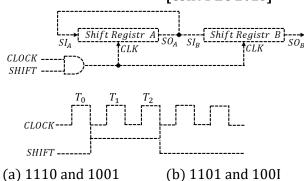

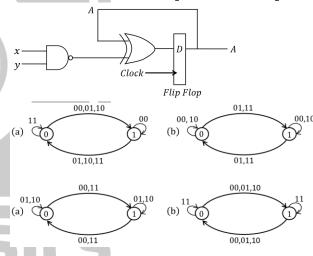

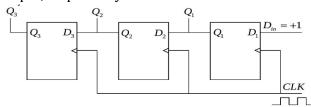

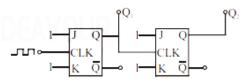

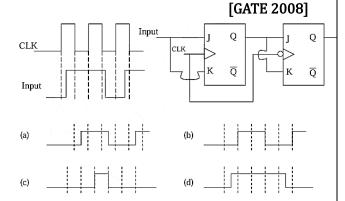

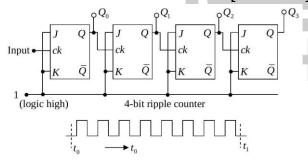

| 3.  | Sequential CKT                          | 73       |  |  |  |  |

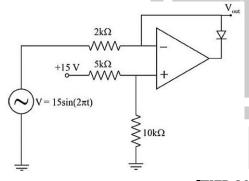

| 4.  | Combinational Circuits                  | 76       |  |  |  |  |

| 5.  | Number System                           | 77       |  |  |  |  |

# **OP-AMP**

# **❖** CSIR-NET PYQ

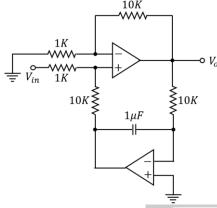

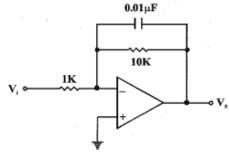

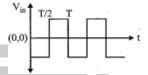

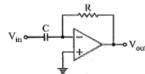

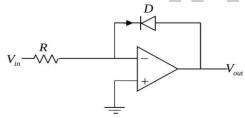

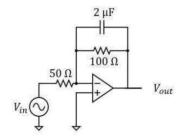

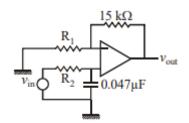

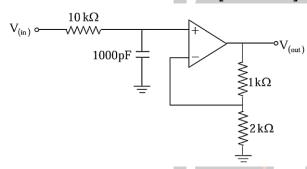

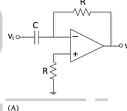

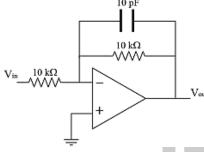

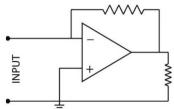

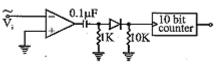

**1.** A time varying signal  $V_{in}$  is fed to an op-amp circuit with output signal  $V_0$  as shown in the figure below.

The circuit implements a [CSIR-JUNE 2011]

- (a) High pass filter with cutoff frequency 16 Hz.

- (b) High pass filter with cutoff frequency 100 Hz

- (c) Low pass filter with cutoff frequency 16 Hz

- (d) Low pass filter with cutoff frequency 100 Hz.

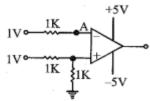

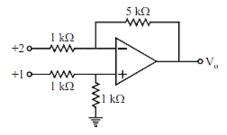

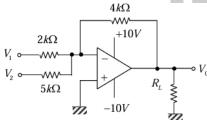

- **2.** In the operational amplifier circuit below, the voltage at point A is

[CSIR-DEC 2011]

- (a) 1.0 V

- (b) 0.5 V

(c) 0 V

- (d) -5.0 V

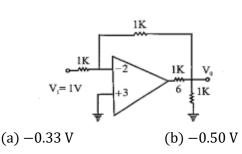

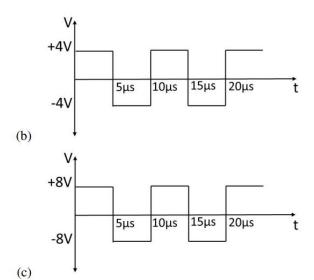

- 3. In the op-amp circuit shown in the figure below, the input voltage  $V_i$  is 1V. The value of the output  $V_0$  is **[CSIR-JUNE 2012]**

- (c) -1.00 V

- (d) -0.25 V

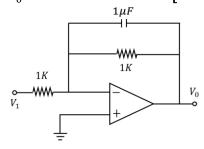

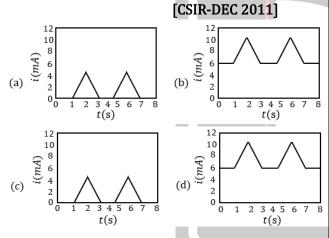

- **4.** In the op-amp circuit shown in the figure,  $V_i$  is a sinusoidal input signal of frequency 10 Hz and  $V_0$  is the output signal.

The magnitude of the gain and the phase shift, respectively, are close to the values

# [CSIR-DEC 2012]

- (a)  $5\sqrt{2}$  and  $\frac{\pi}{2}$

- (b)  $5\sqrt{2}$  and  $\frac{-\pi}{2}$

- (c) 10 and zero

- (d) 10 and  $\pi$

- Band-pass and band-reject filters can be implemented by combining a low pass and a high pass filter in series and in parallel, respectively. If the cut-off frequencies of the low pass and high pass filters are  $\omega_0^{LP}$  and  $\omega_0^{HP}$ , respectively, the condition required to implement the band-pass and band-reject filters are respectively.

[CSIR-DEC 2012]

- (a)  $\omega_0^{\rm HP} < \omega_0^{\rm LP}$  and  $\omega_0^{\rm HP} < \omega_0^{\rm LP}$

- (b)  $\omega_0^{\mathrm{HP}} < \omega_0^{\mathrm{LP}}$  and  $\omega_0^{\mathrm{HP}} > \omega_0^{\mathrm{LP}}$

- (c)  $\omega_0^{\rm HP} > \omega_0^{\rm LP}$  and  $\omega_0^{\rm HP} < \omega_0^{\rm LP}$

- (d)  $\omega_0^{\rm HP} > \omega_0^{\rm LP}$  and  $\omega_0^{\rm HP} > \omega_0^{\rm LP}$

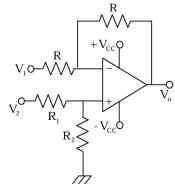

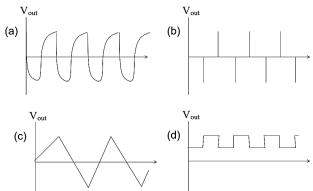

- **6.** Consider the op-amp circuit shown in the figure.

If the input is a sinusoidal wave  $V_i = 5\sin(1000t)$ , then the amplitude of the output  $V_0$  is [CSIR-DEC 2013]

(a)  $\frac{5}{2}$

(b) 5

$(c)^{\frac{5\sqrt{2}}{2}}$

- (d)  $5\sqrt{2}$

- 7. An op-amp based voltage follower [CSIR-JUNE 2014]

- (a) is useful for converting a low impedance source into a high impedance source

- (b) is useful for converting a high impedance source into a low impedance source

- (c) has infinitely high closed loop output impedance

- (d) has infinitely high closed loop gain

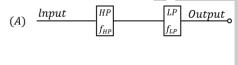

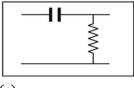

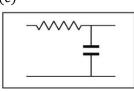

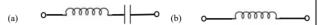

- **8.** Consider a Low Pass (LP) and a High Pass (HP) filter with cut-off frequencies  $f_{LP}$  and  $f_{HP}$  respectively, connected in series or in parallel configurations as shown in the Figures A and B below.

Which of the following statements is correct? [CSIR-DEC 2014]

- (a) For  $f_{HP} < f_{LP}$ , A acts as a Band Pass filter and B acts as a Band Reject filter

- (b) For  $f_{HP} > f_{Lp}$ , A stops the signal from passing through and B passes the signal without filtering

- (c) For  $f_{HP} < f_{LP}$ , A acts as a Band Pass filter and B passes the signal without filtering

- (d) For  $f_{HP} > f_{LP}$ , A passes the signal without filtering and B acts as a Band Reject filter

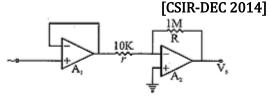

- 9. Consider the amplifier circuit comprising of the two op-amps  $A_1$  and  $A_2$  as shown in the figure If the input ac signal source has an impedance of  $50k\Omega$ , which of the following statements is true?

- (a)  $A_1$  is required in the circuit because the source impedance is much greater than r

- (b)  $A_1$  is required in the circuit because the source impedance is much less than R

- (c)  $A_1$  can be eliminated from the circuit without affecting the overall gain

- (d)  $A_I$  is required in the circuit if the output has to follow the phase of the input signal

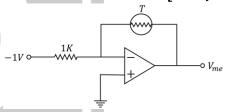

- 10. In the circuit given below, the thermistor has a resistance  $3k\Omega$  at  $25^{\circ}$ C. Its resistance decreases by  $150\Omega$  per °C upon heating. The output voltage of the circuit at  $30^{\circ}$ C is

[CSIR-JUNE 2015]

- (a) -3.75 V

- (b) -2.25 V

- (c) 2.25 V

- (d) 3.75 V

- 11. If the parameters y and x are related by  $y = \log(x)$ , then the circuit that can be used to produce an output voltage  $V_0$  varying linearly with x is [CSIR-DEC 2015]

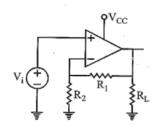

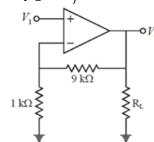

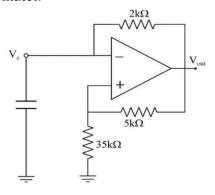

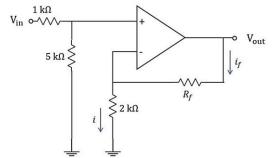

**12.** In the circuit below, the input voltage  $V_i$  is 2 V,  $V_{cc} = 16$  V,  $R_2 = 2$ kΩ and  $R_L = 10$ kΩ.

The value of  $R_f$  required to deliver 10 mW of power across  $R_L$  is **[CSIR-DEC 2016]**

- (a) 12kΩ

- (b) 4Kω

(c)  $8k\Omega$

- (d)  $14k\Omega$

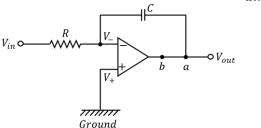

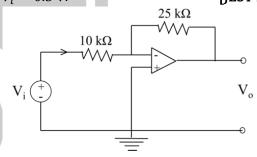

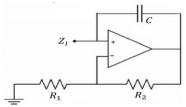

- **13.** The gain of the circuit given below is  $-\frac{1}{\omega RC}$ .

The modification in the circuit required to introduce a dc feedback is to add a resistor

## [CSIR-JUNE 2017]

- (a) between a and b

- (b) between positive terminal of the op-amp and ground

- (c) in series with C

- (d) parallel to C

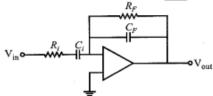

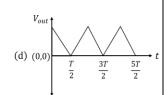

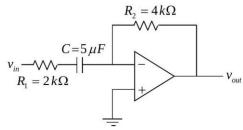

- **14.** In the following operational amplifier circuit  $C_{\rm in}=10{\rm nF}$ ,  $R_{\rm tn}=20{\rm k}\Omega$ ,  $R_F=200{\rm k}\Omega$  and  $C_F=100{\rm pF}$ .

The magnitude of the gain at a input signal frequency of 16kHz is [CSIR-JUNE 2017]

(a) 67

(b) 0.15

(c) 0.3

- (d) 3.5

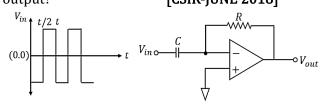

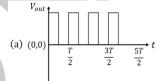

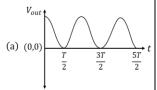

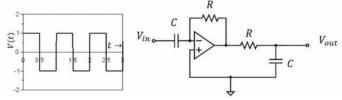

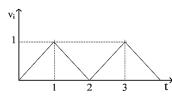

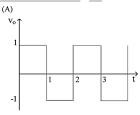

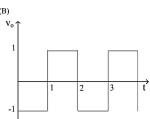

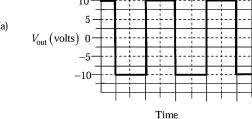

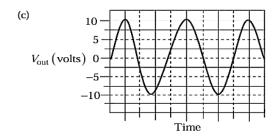

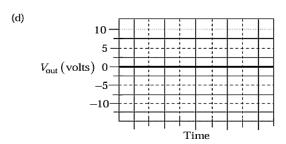

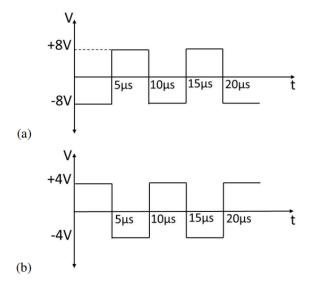

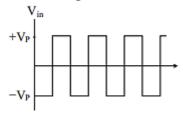

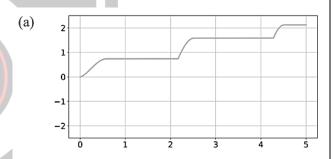

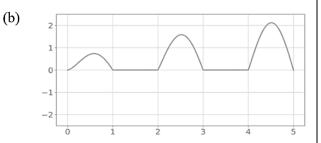

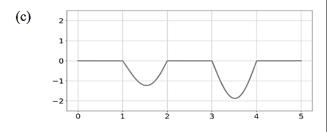

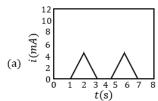

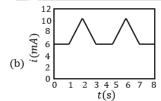

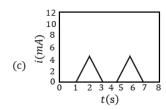

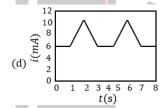

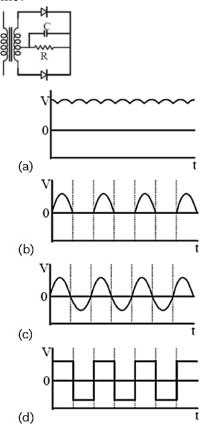

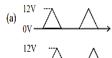

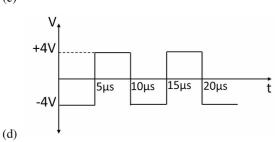

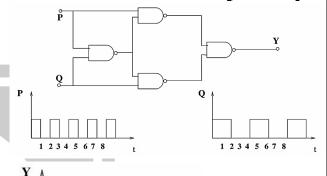

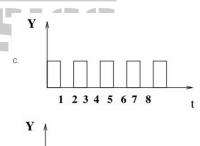

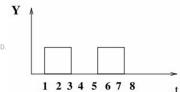

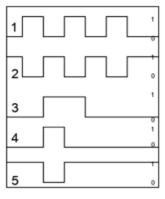

- **15.** The input  $V_i$  to the following circuit is a square wave as shown in the following figure: Which of the waveforms  $V_o$  best describes the output? **[CSIR-JUNE 2018]**

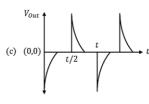

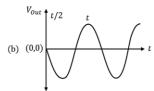

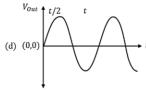

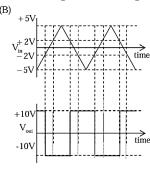

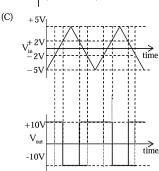

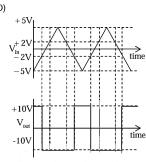

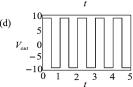

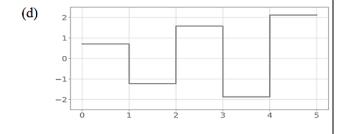

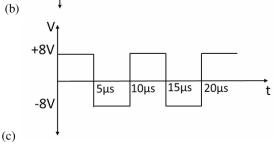

**16.** The input  $V_i$  to the following circuit is a square wave as shown in the following figure.

Which of the waveforms best describes the output?

**17.** For optimal performance of an op-amp based current-to-voltage converter circuit, the input and output impedance should be

# [CSIR-JUNE 2019]

- (a) low input impedance and high output impedance

- (b) low input impedance and low output impedance

- (c) high input impedance and high output impedance

- (d) high input impedance and low output impedance

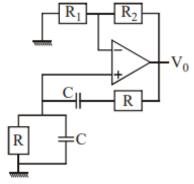

- **18.** A circuit constructed using op-amp, resistor  $R_1=1\mathrm{k}\Omega$  and capacitors  $C_1=1\mu F$  and  $C_2=1\mu F$

$0.1\mu F$ , is shown in the figure below.

This circuit will act as a

[CSIR-JUNE 2019]

- (a) high pass filter

- (b) low pass filter

- (c) band pass filter

- (d) band reject filter

- **19.** In the circuit diagram of a band pass filter shown below,  $R = 10k\Omega$ .

In order to get a lower cut-off frequency of 150 Hz and an upper cut-off frequency of 10kHz, the appropriate values of  $C_1$  and  $C_2$  respectively are [CSIR-DEC 2019]

- (a)  $0.1\mu$ F and 1.5nF

- (b)  $0.3\mu F$  and 5.0nF

- (c) 1.5nF and  $0.1\mu$ F

- (d) 5.0nF and  $0.3\mu$ F

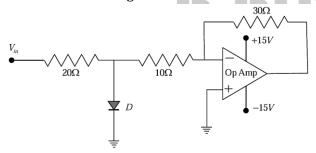

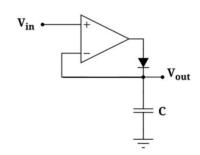

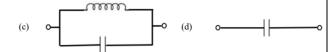

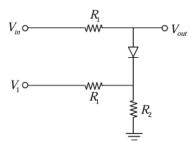

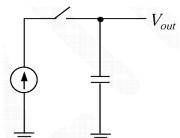

- **20.** The I V characteristics of the diode D in the circuit below is given by

$$I = I_s \left( e^{\frac{qV}{k_B T}} - 1 \right)$$

where  $I_s$  is the reverse saturation current, V is

the voltage across the diode and T is the absolute temperature. If the input voltage is  $V_{\rm in}$ , then the output voltage  $V_{\rm out}$  is

[CSIR-JUNE 2020]

$$(a)I_SR\ln\left(\frac{qV_{\rm in}}{k_BT}+1\right)$$

(b)

$$\frac{1}{q}k_BT\ln\left(\frac{q(V_{in}+I_SR)}{k_BT}\right)$$

$$(c)\frac{1}{q}k_BT\ln\left(\frac{V_{\rm in}}{I_SR}+1\right)$$

(d)

$$-\frac{1}{q}k_BT\ln\left(\frac{V_{in}}{I_SR}+1\right)$$

**21.** In the circuit shown below, the gain of the opamp in the middle of its bandwidth is  $10^5$ . A sinusoidal voltage with angular frequency  $\omega = 100 \text{rad/s}$  is applied to the input of the opamp.

The phase difference between the input and the output voltage is [CSIR-JUNE 2020]

- (a)  $5\pi/4$

- (b)  $3\pi/4$

(c)  $\pi/2$

- (d)  $\pi$

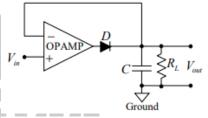

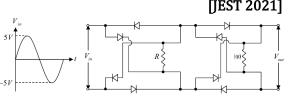

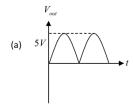

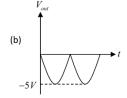

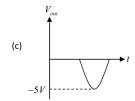

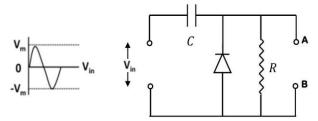

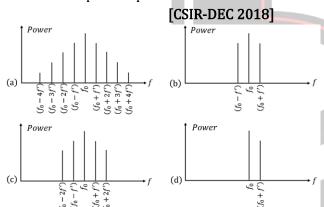

- **22.** In the following circuit the input voltage  $V_{\rm in}$  is such that  $|V_{\rm in}| < |V_{\rm out}|$ , where  $V_{\rm sat}$  is the saturation voltage of the op-amp. (Assume that the diode is an ideal one and  $R_LC$  is much large than the duration of the measure

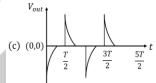

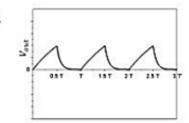

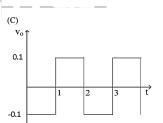

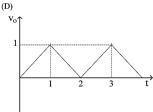

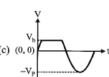

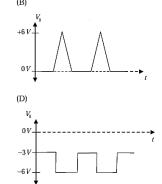

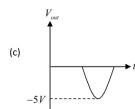

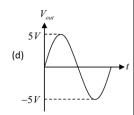

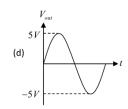

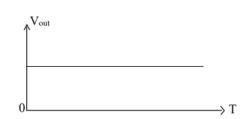

for the input voltage as shown in the figure above, the output voltage  $V_{\rm out}$  is best represented by **[CSIR-JUNE 2021]**

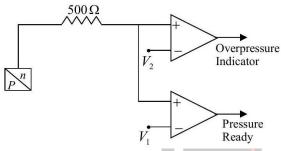

23. The pressure of a gas in a vessel needs be maintained between 1.5 bar to 2.5 bar in an experiment. The vessel is fitted with a pressure transducer that generates 4 mA to 20 mA current for pressure in the range 1 bar to 5 bar. The current output of the transducer has a linear dependence on the pressure.

The reference voltages  $V_1$  and  $V_2$  in the comparators in the circuit (shown in figure above) suitable for the desired operating conditions, are, respectively

# [CSIR-JUNE 2021]

- (a) 2 V and 10 V

- (b) 2 V and 5 V

- (c) 3 V and 10 V

- (d) 3 V and 5 V

- **24.** In the circuit below, there is a voltage drop of 0.7 V across the diode in forward bias while no current flows through it in reverse bias.

In  $V_{\rm in}$  is a sinusoidal signal of frequency 50 Hz with rms value of 1 V the maximum current that flows through the diode is closest to

(a) 1A

(b) 0.14 A

(c) 0 A

- (d) 0.07 A

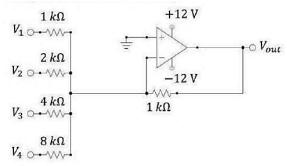

- **25.** In the circuit shown below using an ideal op amp, inputs  $V_j$  (j = 1,2,3,4) may either be open or connected to a 5 V battery.

The minimum measurement range of a voltmeter to measure all possible values of  $V_{\rm out}$  is **[CSIR-DEC 2023]**

(a)10 V

(b)30 V

(c)3 V

- (d)1 V

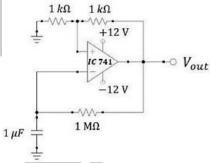

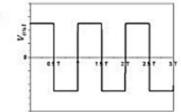

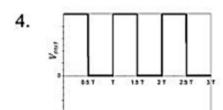

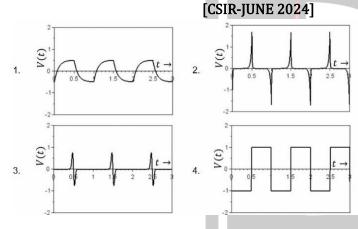

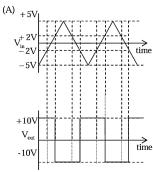

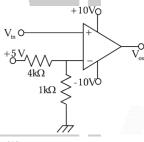

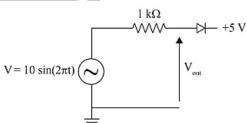

- **26.** A circuit with operational amplifier is shown in the figure below.

The output voltage waveform  $V_{\text{out}}$  will be closest to **[CSIR-DEC 2023]**

1.

2.

3.

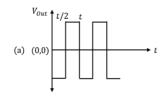

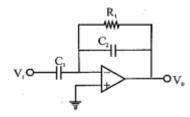

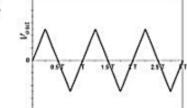

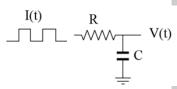

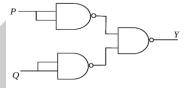

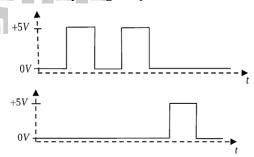

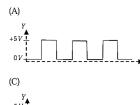

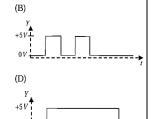

**27.** A train of square wave pulses is given to the input of an ideal opamp circuit shown below.

Given that the time period of the input pulses  $T \ll RC$  and the opamp does not get into saturation, which of the following best represents the output waveform?

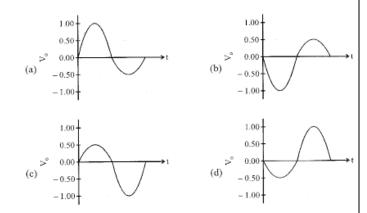

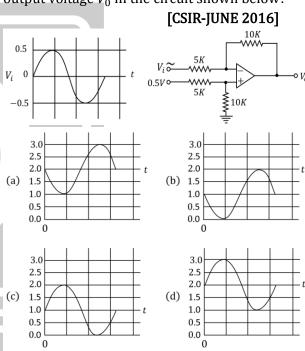

**28.** Given the input voltage  $V_i$ , which of the following waveforms correctly represents the output voltage  $V_0$  in the circuit shown below?

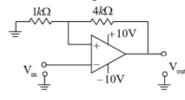

**29.** In the circuit shown below, the input voltage (in volts) is given by

$$\begin{split} V_{in}(t) &= 0.1\mathrm{sin}\left(\omega_1 t\right) + \mathrm{sin}\left(\omega_2 t\right) \\ \text{where } \omega_1 &= 5\times 10^2 \; \mathrm{s}^{-1} \; \mathrm{and} \; \omega_2 = 5\times 10^4 \; \mathrm{s}^{-1}. \end{split}$$

The time varying part of the output voltage  $V_{\rm out}(t)$  (in volts) is closest to [CSIR DEC 2024] (a)-0.2sin  $(\omega_1 t)$  - 2sin  $(\omega_2 t)$

(b)

$$-0.2\sin(\omega_1 t) + 0.2\cos(\omega_2 t)$$

$$(c)2\cos{(\omega_1 t)} + 0.2\cos{(\omega_2 t)}$$

(d)2cos (

$$\omega_1 t$$

) – 2sin ( $\omega_2 t$ )

# GATE PYQ

1. The inverting input terminal of an operational amplifier (op-amp) is shorted with the output terminal apart from being grounded. A voltage signal  $v_i$  is applied to the non-inverting input terminal of the op-amp. Under this configuration, the op-amp functions as

[GATE 2004]

- (a) an open loop inverter

- (b) a voltage to current converter

- (c) a voltage follower

- (d) an oscillator

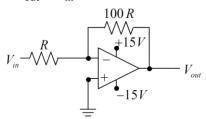

- 2. Figure shows a practical integrator with  $R_S = 30 \text{M}\Omega$ ,  $R_F = 20 \text{M}\Omega$  and  $C_F = 0.1 \mu\text{F}$ . If a step (dc) voltage of +3 V is applied as input for  $0 \le t \le 4$  ( t is in seconds), the output voltage is [GATE 2004]

$R_{S}$   $R_{S}$   $R_{OM}$

(a) a ramp function of -6 V

- (b) a step function of -12 V

- (c) a ramp function of -15 V

- (d) a ramp function of -4 V

- 3. The output  $V_0$  of the ideal opamp circuit shown in the figure is **[GATE 2005]**

- (a) -7 V

- (b) -5 V

(c) 5 V

- (d) 7 V

- 4. The circuit shown in the figure can be used as a [GATE 2005]

- (a) high pass filter or a differentiator

- (b) high pass filter or an integrator

- (c) low pass filter or a differentiator

- (d) low pass filter or an integrator

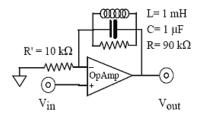

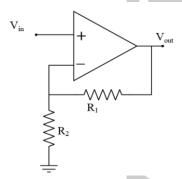

- **5.** The low-pass active filter shown in the figure has a cut-off frequency of 2kHz and a pass band gain of 1.5. The values of the resistors are

[GATE 2006]

- (a)  $R_1 = 10k\Omega$ ;  $R_2 = 1.3\Omega$

- (b)  $R_1 = 30k\Omega$ ;  $R_2 = 1.3\Omega$

- (c)  $R_1 = 10k\Omega$ ;  $R_2 = 1.7\Omega$

(d)

$$R_1 = 30k\Omega$$

;  $R_2 = 1.7\Omega$

- **6.** In order to obtain a solution of the differential equation  $\frac{d^2v}{dt^2} 2\frac{dv}{dt} + v_1 = 0$ , involving voltages v(t) and  $v_1$ , an operational amplifier (Op-Amp) circuit would require at least **[GATE 2006]**

- (a) two Op-Amp integrators and one Op-Amp adder

- (b) two Op-Amp differentiators and one Op-Amp adder

- (c) one Op-Amp integrator and one Op-Amp adder

- (d) one Op-Amp integrator, one Op-Amp differentiator and one Op-Amp adder

- 7. The circuit shown is based on ideal operational amplifiers. It acts as a [GATE 2007]

- (a) subtractor

- (b) buffer amplifier

- (c) adder

- (d) divider

# Statement for Linked Answer Questions 8 &9:

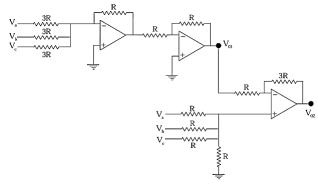

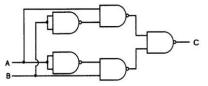

The following circuit contains three operational amplifiers and resistors.

- 8. The output voltage at the end of second operational amplifier  $V_{01}$  is **[GATE 2008]** (a)  $V_{01} = 3(V_a + V_b + V_c)$

(b)

$$V_{01} = -\frac{1}{3}(V_a + V_b + V_c)$$

(c)

$$V_{01} = \frac{1}{3}(V_a + V_b + V_c)$$

(d)

$$V_{01} = \frac{4}{3}(V_a + V_b + V_c)$$

9. The output  $V_{02}$  (at the end of third op amp) of the above circuit is **[GATE 2008]**

(a)

$$V_{02} = 2(V_a + V_b + V_c)$$

(b)

$$V_{02} = 3(V_a + V_b + V_c)$$

(c)

$$V_{02} = -\frac{1}{2}(V_a + V_b + V_c)$$

- (d) zero

- **10.** The Common Mode Rejection Ratio (CMRR) of a differential amplifier using an operational amplifier is 100 dB. The output voltage for a differential input of  $200\mu V$  is 2 V. The common mode gain is **[GATE 2009]**

- (a) 10

(b) 0.1

(B)

- (c) 30 Db

- (d) 10 dB

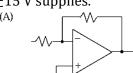

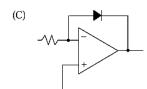

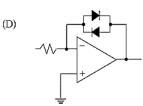

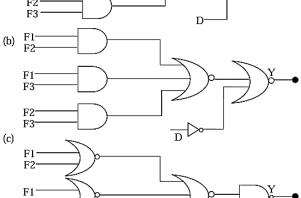

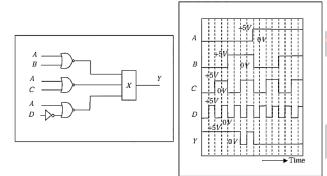

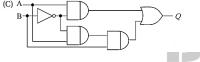

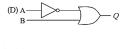

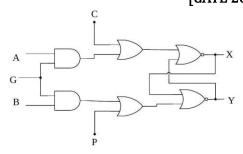

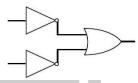

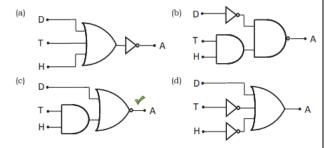

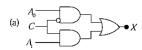

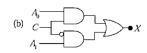

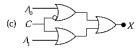

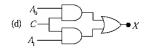

- 11. In one of the following circuits, negative feedback does not operate for a negative input. Which one is it? The op-amps are running from ±15 V supplies. [GATE 2010]

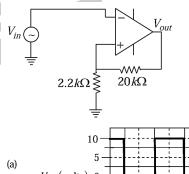

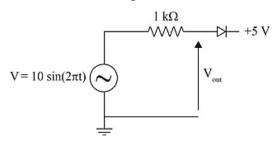

12. Consider the following circuit

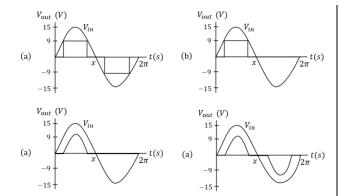

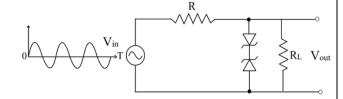

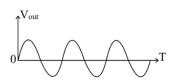

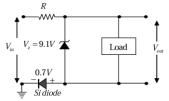

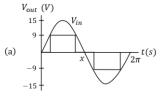

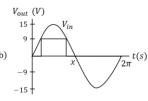

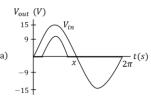

Which of the following correctly represent the output  $V_{\text{out}}$  corresponding to the input  $V_{\text{in}}$ ?

[GATE 2011]

**13.** Consider the following OP-AMP circuit

[GATE 2012]

**14.** In the following circuit, for the output voltage to be  $V_0 = (-V_1 + V_2/2)$ , the ratio  $R_1/R_2$  is

[GATE 2012]

(a) ½

(b) 1

(c) 2

(d)3

Statement for Linked Answer Questions 15 and 16: Consider the following circuit

[GATE 2013]

- **15.** For this circuit the frequency above which the gain will decreases by 20 dB per decade is

- (a) 15.9kHz

- (b) 1.2kHz

- (c) 5.6kHz

- (d) 22.5kHz

- **16.** At 1.2kHz the closed loop gain is

- (a) 1

(b) 1.5

(c) 3

- (d) 0.5

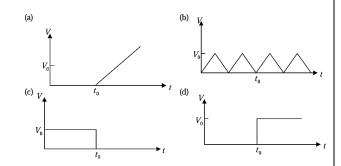

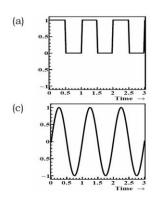

- **17.** The input given to an ideal OP-AMP integrator circuit is **[GATE 2014]**

The correct output of the integrator circuit is

**18.** A low pass filter is formed by a resistance R and a capacitance C. At the cut off angular frequency  $\omega_c = \frac{1}{RC}$ , the voltage gain and the phase of the output voltage relative to the input voltage respectively are **[GATE 2014]**

(a) 0.71 and 45°

(b)  $0.71 \text{ and } -45^{\circ}$

(c)  $0.5 \text{ and } -90^{\circ}$

- (d) 0.5 and 90°s

- **19.** Consider the circuit shown in the figure, where RC = 1. For an input signal  $V_i$  shown below, choose the correct  $V_0$  from the options:

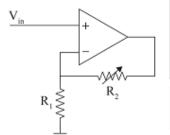

[GATE 2015]

**20.** In the given circuit, if the open loop gain  $A = 10^5$ , the feedback configuration and the closed loop gain  $A_f$  are **[GATE 2015]**

- (a) series-shunt,  $A_f = 9$

- (b) series-series,  $A_f = 10$

- (c) series-shunt,  $A_f = 10$

- (d) shunt-shunt,  $A_f = 10$

- 21. Consider an ideal operational amplifier as shown in the figure below with  $R_1=5k\Omega$ ,  $R_2=1k\Omega$ ,  $R_L=100k\Omega$ . For an applied input voltage V=10mV, the current passing through  $R_2$  is \_\_\_\_\_  $\mu A$ . (up to two decimal places)

[GATE 2017]

**22.** For an operational amplifier (ideal) circuit shown below,

If  $V_1 = 1V$  and  $V_2 = 2V$ , the value of  $V_0$  is V (up to one decimal place). **[GATE 2018]**

**23.** For the following circuit, what is the magnitude of  $V_{out}$  if  $V_{in} = 1.5 \text{ V}$ ? **[GATE 2019]**

- (a) 0.015 V

- (b) 0.15 V

- (c) 15 V

- (d) 150 V

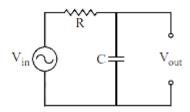

- **24.** The input voltage  $(V_{in})$  to the circuit shown in the figure is  $2\cos{(100t)}V$ . The output voltage  $(V_{out})$  is  $2\cos{\left(100t-\frac{\pi}{2}\right)}V$ . If  $R=1k\Omega$ , the value of C (in  $\mu F$ ) is **[GATE 2020]**

(a) 0.1

(b) 1

(c) 10

- (d) 100

- **25.** For an Op-Amp based negative feedback, non-inverting amplifier, which of the following statements are true?

[GATE 2022]

- (a) Closed loop gain < Open loop gain

- (b) Closed loop bandwidth < Open loop bandwidth

- (c) Closed loop input impedance > Open loop input impedance

- (d) Closed loop output impedance < Open loop output impedance

- **26.** For the Op-Amp circuit shown below, choose the correct output waveform corresponding to the input  $V_{in} = 1.5\sin 20\pi t$  (in Volts). The saturation voltage for this circuit is  $V_{\text{sat}} = \pm 10 \text{ V}$ .

[GATE 2022]

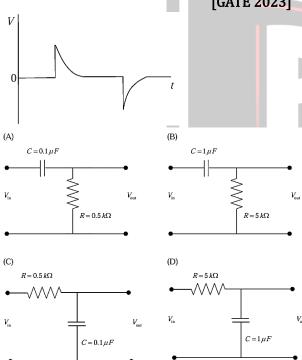

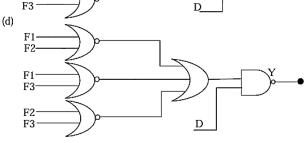

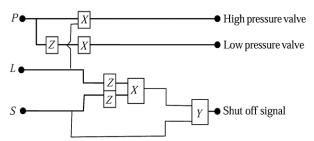

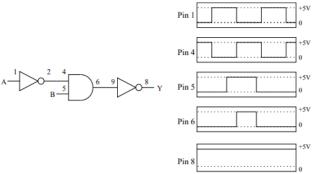

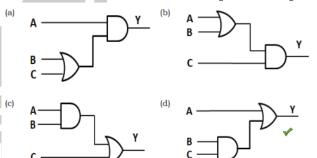

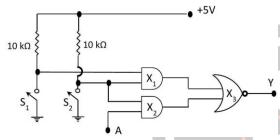

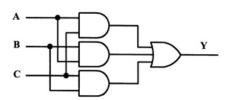

**27.** An input voltage in the form of a square wave of frequency 1kHz is given to a circuit, which results in the output shown schematically below. Which one of the following options is the CORRECT representation of the circuit?

[GATE 2023]

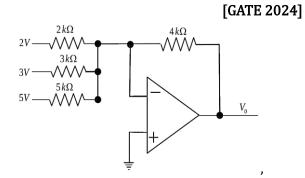

**28.** Consider the operational amplifier circuit shown in figure.

The output voltage  $V_0$  is V (integer).

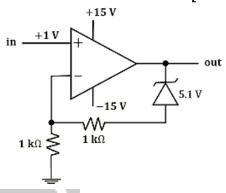

**29.** The figure shows an opamp circuit with a 5.1 V Zener diode in the feedback loop. The opamp runs from  $\pm 15$  V supplies. If a +1 V signal is applied at the input, the output voltage (rounded off to one decimal place) is

[GATE 2025]

## **❖** JEST PYQ

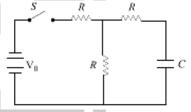

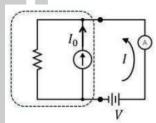

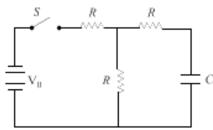

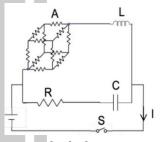

1. A capacitor C is connected to a battery  $V_0$  through three equal resistors R and a switch S as shown below:

The capacitor is initially uncharged. At time t=0, the switch S is closed. The voltage across the capacitor as a function of time ' t ' for t>0 is given by [JEST 2012]

(a)

$$(V_0/2)(1 - \exp(-t/2Rc))$$

(b)

$$(V_0/3)(1 - \exp(-t/3Rc))$$

(c)

$$(V_0/3)(1 - \exp(-3t/2Rc))$$

(d)

$$(V_0/2)(1 - \exp(-2t/3Rc))$$

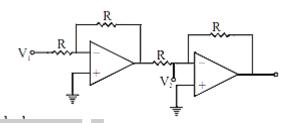

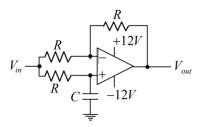

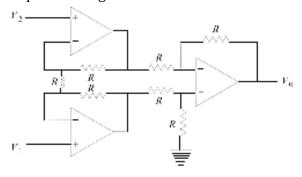

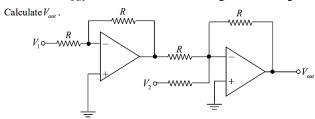

**2.** The classic three op-amp instrumentation amplifier configuration is shown below:

The op-amp are ideal and all resistors are of equal value R. The gain, defined as the output voltage  $V_0$  divided by the differential input voltage  $V_1-V_2$ , is equal to **[JEST 2012]**

(a) 2

(b) 3

(c) 4

(d) 6

**3.** What is the voltage at the output of the following operational amplifier circuit [see figure 1]?

[JEST 2015]

(a) 1 V

(b) 1Mv

(c) 1μV

(d) 1Nv

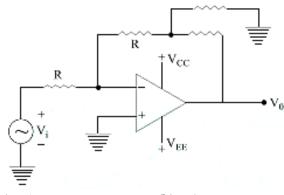

4. Consider a 741 operational amplifier circuit as shown below, where  $V_{CC} = V_{EE} = +15V$  and  $R = 2.2k\Omega$ . If  $V_1 = 2$ mV, what is the value of  $V_0$  with respect to the ground? [JEST 2017]

(a) -1mV

(b) -2mV

(c) -3mV

(d) -4mV

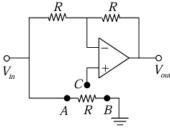

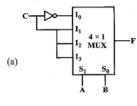

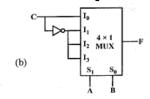

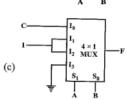

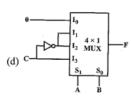

5. Analysis the ideal op-amp circuit in the figure. Which one of the following statements is true about the output voltage  $V_{\rm out}$ , when terminal 'C' is connected to point 'A' and then to point 'B'? [JEST 2019]

- $(a)V_{\rm out} = V_{\rm in}$  and  $V_{\rm out} = -V_{\rm in}$  when ' C ' is connected to ' A ' and ' B ', respectively

- (b)  $V_{\text{out}} = -V_{\text{in}}$  and  $V_{\text{out}} = V_{\text{in}}$  when ' C ' is connected to ' A ' and ' B ', respectively

- (c)  $V_{\text{out}} = -V_{\text{in}}$  when ' C ' is connected to either ' A ' or ' B '

- (d)  $V_{\text{out}} = V_{\text{in}}$  when ' C ' is connected to either ' A ' or ' B '

- **6.** Analyse the op-amp circuit shown in the figure below. What is the output voltage  $(V_0)$  in millivolts if  $V_1 = 2.5$  and  $V_2 = 2.25$  V?

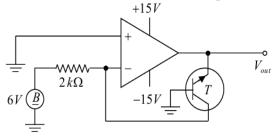

7. An ideal op-amp and a silicon transistor T are used in the following circuit. Find the output voltage  $V_{\rm out}$  [JEST 2021]

(a) +5.3 V

(b) -0.7 V

(c) + 0.7 V

(d) - 15 V

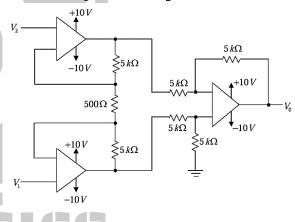

8. In the figure below with ideal op-amps, the value of  $R=10 \mathrm{k}\Omega$ ,  $V_1=-10 \mathrm{mV}$ , and  $V_2=-30 \mathrm{mV}$ .

Calculate  $V_{\rm out}$ .

[JEST 2021]

- (a) +40mV

- (b) -40mV

- (c) + 20mV

- (d) -20mV

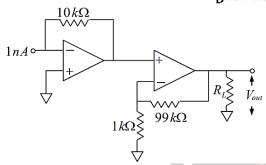

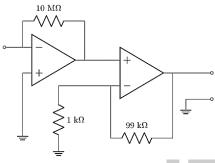

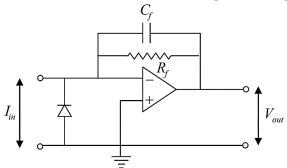

- **9.** What is the output voltage of the following circuit for the input current 1nA? **[JEST 2022]**

- (a) 1mV

- (b) 1 V

(c) 1µV

- (d) 1Nv

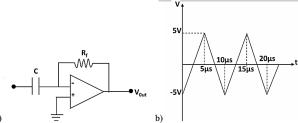

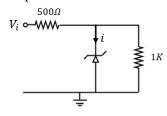

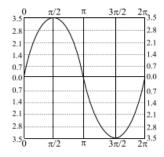

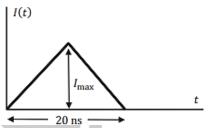

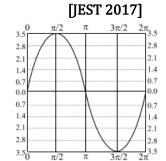

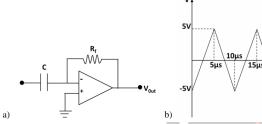

- 10. Consider the Op-Amp differentiator presented in Figure (a). Take  $C=0.002\mu F$  and  $R_f=2 k\Omega$ . For a triangular wave input shown in the figure (b), [JEST 2023]

determine the output voltage waveform.

11. What is the output voltage  $V_o$  and current I in the  $10 \text{k}\Omega$  resistance of the following circuit?  $V_i = 0.5 \text{ V}$ . [JEST 2024]

(a)

$$V_o = -1.25 \text{ V}$$

,  $I = 20 \mu \text{A}$

(b)

$$V_0 = -0.4 \text{ V}, I = 50 \mu \text{A}$$

(c)

$$V_o = -0.4 \text{ V}$$

,  $I = 20 \mu \text{A}$

(d)

$$V_o = -1.25$$

V, I = 50µA

## TIFR PYQ

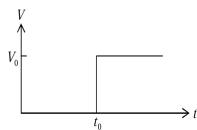

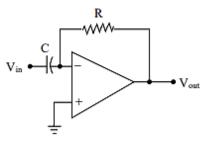

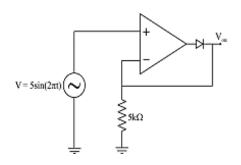

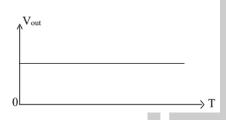

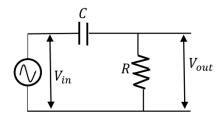

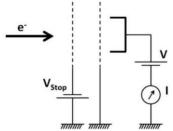

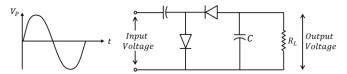

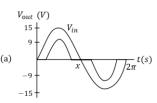

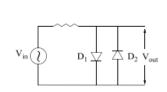

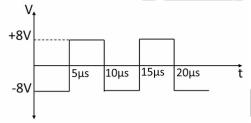

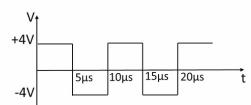

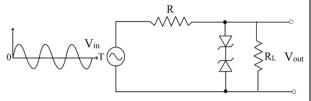

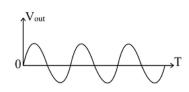

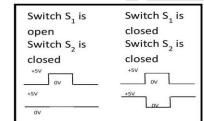

**1.** Consider the following circuit:

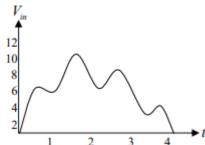

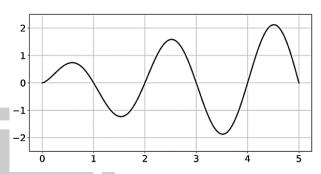

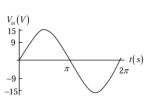

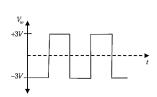

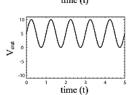

If the waveform given below is fed in at  $V_{in}$ ,

then the waveform at the output  $V_{\text{out}}$  will be

[TIFR 2012]

2. An input of 1.0 VDC is given to the ideal Op-Amp circuit depicted below. What will be the output voltage? [TIFR 2013]

(a) 10.0 V

(b) -9.0 V

(c) 1.0 V V

(d) 0 V

3. In the following circuit, the resistance  $R_2$  is doubled.

It follows that the current through  $R_2$

[TIFR 2014]

(a) remains the same.

(b) is halved.

(c) is doubled.

(d) is quadrupled.

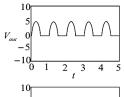

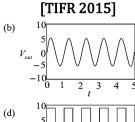

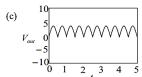

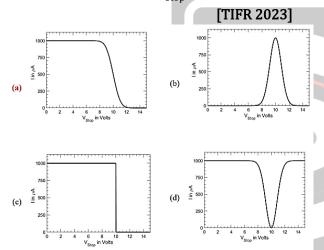

**4.** In the circuit shown below, the op-amp is powered by a bipolar supply of  $\pm 10$  V.

Which one of the following graphs represents

V<sub>out</sub> correctly?

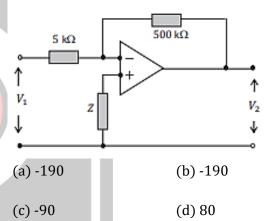

5. In the generalized operational amplifier circuit shown on the right, the op. amp. has a very high input impedance ( $Z>50\mathrm{M}\Omega$ ) and an open gain of 1000 for the frequency range under consideration. Assuming that the op. amp. draws negligible current, the voltage ratio  $V_2/V_1$  is approximately [TIFR 2016]

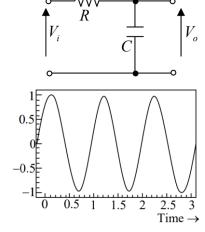

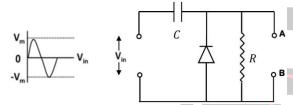

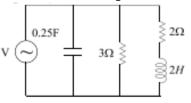

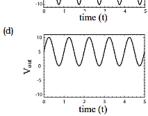

**6.** For the circuit depicted on the right, the input voltage  $V_i$  is a simple sinusoid as shown below, where the time period is much smaller compared to the time constant of this circuit.

[TIFR 2016]

The voltage  $V_o$  across C is best represented by

7. The following circuit is fed with an input sine wave of frequency 50 Hz.

Which of the following graphs (solid line is input and dashed line is output) best represents the correct situation?

[TIFR 2017]

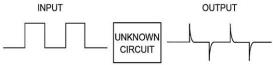

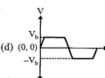

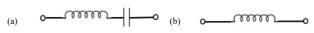

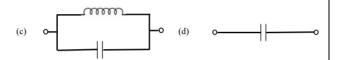

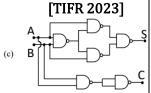

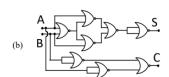

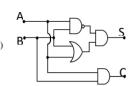

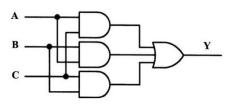

The figure below shows an unknown circuit, with an input and output voltage signal.

From the form of the input and output signals, one can infer that the circuit is likely to be

[TIFR 2018]

(c)

(d)

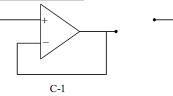

**9.** Consider the following circuits C-1 and C-2.

You can apply the golden rules of an ideal op-[TIFR 2018] amp to

- (a) only C-1

- (b) only C-2

- (c) both C-1 and C-2

- (d) neither C-1 nor C-2

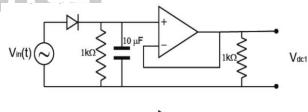

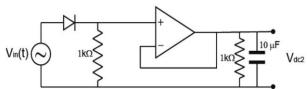

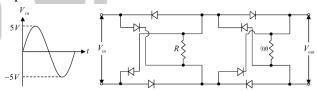

- **10.** A signal  $V_{in}(t) = 5\sin(100\pi t)$  is sent to both the circuits sketched below.

If the *DC* output voltage of the top circuit has a value  $V_{dc1}$  and the bottom circuit has a value  $V_{\rm dc2}$ , then which of the following statements about the relative value of  $V_{dc1}$  and  $V_{dc2}$  is correct? [TIFR 2018]

(a)  $V_{dc1} < V_{dc2}$

- $(b)V_{dc1} > V_{dc2}$

- $(c)V_{dc1} = V_{dc2}$

- (d) It will depend on the slew rate of the opamp.

- **11.** Consider the following circuit. **[TIFR 2019]**

It is given that  $C_f = 100 \, \mathrm{pF}$ , and for  $I_{\mathrm{in}} = 50 \, \mathrm{nA}$  D.C.,  $V_{\mathrm{out}} = 1 \, \mathrm{V}$  D.C. Therefore, the bandwidth of the above circuit is

- (a) 15.8 Hz

- (b) 79.6 Hz

- (c) 145.3 Hz

- (d) 200.4 Hz

- **12.** In the above circuit, which of the following is the maximum value, in Volts, of voltage at  $V_{\text{out}}$ ?

[TIFR 2020]

(a) 10

(b) 15

(c) 0

- (d)5

- **13.** The circuit sketched below is called a relaxation oscillator.

For the parameters indicated in the figure, the ratio of the maximum voltage at  $V_{\rm out}$  to the maximum voltage at  $V_c$  is **[TIFR 2020]**

(a) 1/8

(b) 1/7

(c) 2/7

- (d) 1/4

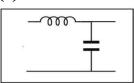

- **14.** An operational amplifier is configured as shown in the figure below. For an AC input this circuit behaves effectively as **[TIFR 2021]**

- (a) a resistor with a negative resistance.

- (b) an inductor with a negative inductance.

- (c) a capacitor with a negative capacitance.

- (d) an inductor with a positive inductance

- **15.** Consider the following circuit with an op-amp.

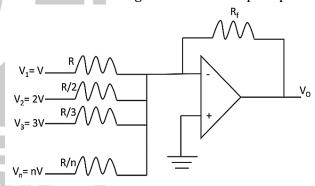

If the output voltage  $V_0$  is measured to be  $V_0 = -V$ , then the value of the feedback resistance  $R_f$  must be **[TIFR 2021]**

$$(a)R_f = nR$$

(b)

$$R_f = \frac{3R}{n(n+1)(2n+1)}$$

(c)

$$R_f = \frac{6R}{n(n+1)(2n+1)}$$

(d)

$$R_f = R/n$$

16

**16.** Consider a circuit with an operational amplifier (op amp) and four resistors as sketched below.

The output voltage  $V_0$  is

[TIFR 2022]

(a)

$$-12 \text{ V}$$

$$(c) - 9 V$$

$$(d) - 6 V$$

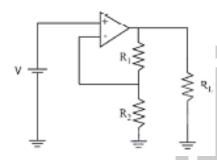

**17.** The non-inverting amplifier shown in the figure on the right is constructed using a nonideal operational amplified (op amp) with a finite open loop gain *A*.

The value of feedback fraction is

$$B = \frac{R_2}{R_1 + R_2} = 0.1$$

If the gain *A* varies such that

$$10^4 < A < 10^5$$

then the approximate percentage variation in

the closed loop gain will be.

[TIFR 2022]

- (a) 0.09%

- (b) 0.0%

- (c) 0.9%

- (d) 9.0%

- **18.** At what value of  $R_f$  will the ideal op-amp shown in the figure provide a gain of 6? **[TIFR 2023]**

- (a)  $22.5k\Omega$

- (b)  $19.5k\Omega$

- (c) 12.4kΩ

- (d)  $14.4k\Omega$

**19.** For the circuit on the right, which graph represents  $V_{\text{out}}$  correctly for the  $V_{\text{in}}$  shown below? **[TIFR 2025]**

|          | Α.    | 1         |       |         |  |  |  |

|----------|-------|-----------|-------|---------|--|--|--|

|          |       | nswers ke | У     |         |  |  |  |

| CSIR-NET |       |           |       |         |  |  |  |

| 1. a     | 2. a  | 3. c      | 4. d  | 5. b    |  |  |  |

| 6. c     | 7. b  | 8. a      | 9. a  | 10. c   |  |  |  |

| 11. c    | 12. c | 13. d     | 14. d | 15. b   |  |  |  |

| 16. c    | 17. b | 18. a     | 19. a | 20. d   |  |  |  |

| 21. a    | 22. a | 23. d     | 24. c | 25. a   |  |  |  |

| 26. a    | 27. d | 28. b     | 29. b |         |  |  |  |

|          | GATE  |           |       |         |  |  |  |

| 1. c     | 2. d  | 3. a      | 4. d  | 5. d    |  |  |  |

| 6. a     | 7. b  | 8. c      | 9. d  | 10. b   |  |  |  |

| 11. c    | 12. a | 13. a     | 14. d | 15. a   |  |  |  |

| 16. b    | 17. a | 18. b     | 19. b | 20. с   |  |  |  |

| 21. 1    | 223.6 | 23. с     | 24. c | 25. acd |  |  |  |

| 26. a    | 27. a | 2812      | 29.   |         |  |  |  |

|          |       | JEST      |       |         |  |  |  |

| 1. d     | 2. b  | 3. b      | 4. c  | 5. a    |  |  |  |

| 6. 5250  | 7. b  | 8. c      | 9. b  | 10. a   |  |  |  |

| 11. d    |       |           |       |         |  |  |  |

| TIFR     |       |           |       |         |  |  |  |

| 1. b     | 2. c  | 3. a      | 4. d  | 5. c    |  |  |  |

| 6. c     | 7. c  | 8. b      | 9. a  | 10. b   |  |  |  |

| 11. b    | 12. a | 13. a     | 14. c | 15. c   |  |  |  |

| 16. c    | 17. c | 18. c     | 19. a |         |  |  |  |

|          |       |           |       |         |  |  |  |

D PHYSICS

# **Network Theory & Circuit Analysis**

1. A resistance is measured by passing current through it and measuring the resulting voltage drop. If the voltmeter and the ammeter have uncertainties of 3% and 4%, respectively, then (A) The uncertainty in the value of resistance is

[CSIR-JUNE 2011]

- (a) 7.0%

- (b) 3.5%

- (c) 5.0%

- (d) 12.0%

- (B) The uncertainty in the computed value of the power dissipated in resistance is

- (a) 7%

- (b) 5%

- (c) 11%

- (d) 9%

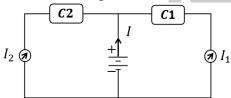

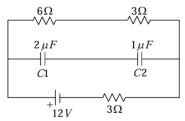

- **2.** A battery powers two circuits  $C_1$  and  $C_2$  as shown in t the figure

The total current I drawn from the battery is estimated by measuring the currents  $I_1$  and  $I_2$  through the individual circuits. If  $I_1$  and  $I_2$  are both 200 mA and if the errors in their measurement are 3 mA and 4 mA respectively, the error in the estimate of 1 is:

[CSIR-DEC 2011]

- (a) 7.0 mA

- (b) 7.5 Ma

- (c) 5.0 mA

- (d) 10.5 mA

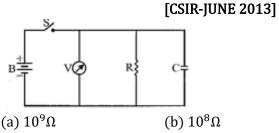

- 3. The insulation resistance R of an insulated cable is measured by connecting it in parallel with a capacitor C, a voltmeter, and battery B as shown. The voltage across the cable dropped from 150 V to 15 V, 1000 seconds after the switch S is closed. If the capacitance of the cable is  $5\mu F$  then its insulation resistance is approximately

- (c)  $10^{7}\Omega$

- (d)  $10^{6}\Omega$

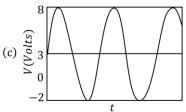

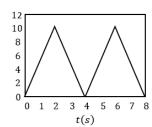

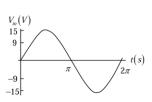

- **4.** An ac signal of the type as shown in the figure, is applied across a resistor  $R = 1\Omega$ .

The power dissipated across the resistor is

[CSIR-JUNE 2019]

- (a) 12.5 W

- (b) 9 W

- (c) 25 W

- (d) 21.5 W

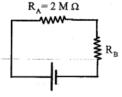

- **5.** Two voltmeters A and B with internal resistances  $2M\Omega$  and  $0.1k\Omega$  are used to measure the voltage drops  $V_A$  and  $V_B$ , respectively, across the resistor R in the circuit shown below.

The ratio  $V_A/V_B$  is

[CSIR-JUNE 2020]

- (a) 0.58

- (b) 1.73

(c) 1

- (d) 2

- 6. An inductor L, a capacitor C and a resistor R are connected in series to an AC source,  $V = V_0 \sin \omega t$ . If the net current is found to depend only on R, then [CSIR-NOV 2020]

- (a) C = 0

- (b) L = 0

(c)

$$\omega = 1/\sqrt{LC}$$

(d)  $\omega = \sqrt{\frac{1}{LC} - \frac{R^2}{4L^2}}$

7. A circuit needs to be designed to measure the resistance R of a cylinder PQ to the best possible accuracy, using an ammeter A, a voltmeter V, a battery E and a current source  $I_S$  (all assumed to be ideal). The value of R is known to be approximately  $10\Omega$ , and the resistance W of each of the connecting wires is close to  $10\Omega$ . If the current from the current source and voltage from the battery are known exactly, which of the following circuits provides the most accurate measurement of R?

# [CSIR-JUNE 2023]

(a) B

(b) A

(c) C

- (d) A

- 8. A train of impulses of frequency 500 Hz, in which the temporal width of each spike is negligible compared to its period, is used to sample a sinusoidal input signal of frequency 100 Hz. The sampled output is

## [CSIR-JUNE 2023]

- (a) Discrete with the spacing between the peaks being the same as the time period of the sampling signal

- (b) a sinusoidal wave with the same time period as the sampling signal

- (c) discrete with the spacing between the peaks being the same as the time period of the input signal

- (d) a sinusoidal wave with the same time period as the input signal

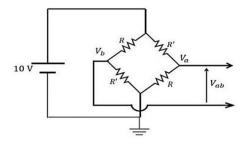

- 9. In the circuit shown in the figure, the resistances R and R' change due to strain. While R increases, R' decreases by the same amount  $\Delta R$  due to the applied strain. The unstrained values of R and R' are  $100\Omega$  each. If same strain is applied to all the resistors, and the output voltage  $(V_{ab})$  changes to 0.3 V, then  $\Delta R$  is closest to

#### [CSIR JUNE 2024]

- (a)  $3\Omega$  (b)  $1.5\Omega$

- (c)  $4.5\Omega$  (d)  $6\Omega$

- 10. A battery with an open circuit voltage of 10 V is connected to a load resistor of  $485\Omega$  and the voltage measured across the battery terminals using an ideal voltmeter is 9.7 V . The internal resistance of the battery is closest to

# [CSIR JUNE 2024]

$(a)30\Omega$

$(b)15\Omega$

$(c)20\Omega$

- $(d)40\Omega$

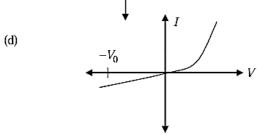

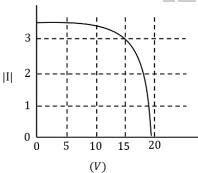

- **11.** A circuit component consists of a resistor in parallel with an ideal current source. The I-V characteristics of the component was measured using a variable voltage source and an ammeter A'.

The arrow in the figure indicates the positive direction of current. The I-V characteristics of the component is best represented by

#### [CSIR DEC 2024]

1.

2.

3.

#### **❖** GATE PYQ

1. A resistance of  $600\Omega$  is parallel to an inductance of reactance  $600(\Omega)$  applied voltage, then the total impedance of the circuit is

[GATE 2001]

- (a)  $628\Omega$

- (b) 268Ω

- (c)  $424\Omega$

- (d)  $300\Omega$

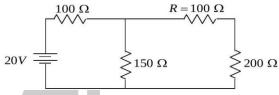

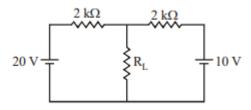

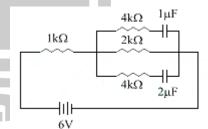

- **2.** In the circuit shown in the figure the Thevenin voltage  $V_{Th}$  and Thevenin resistance  $R_{Th}$  as

seen by the load resistance  $R_L (= 1k\Omega)$  are respectively [GATE 2005]

- (a) 15 V,  $1k\Omega$

- (b) 30 V, 4kΩ

- (c)  $20 \text{ V}, 2k\Omega$

- (d)  $10 \text{ V}, 5\text{K}\omega$

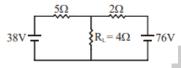

- 3. For the circuit shown, the potential difference (in Volts) across  $R_L$  is **[GATE 2007]**

(a) 48

(b) 52

(c) 56

- (d) 65

- **4.** An a. c. voltage of 220  $V_{ms}$  is applied to the primary of a 10:1 step-down transformer. The secondary of the transformer is centre lapped and connected to a full wave rectifier with a load resistance. The d. c. voltage appearing across the load is

[GATE 2008]

(a)  $\frac{22}{\pi}$

(b)  $\frac{31}{\pi}$

$(c)\frac{62}{\pi}$

- (d)  $\frac{44}{\pi}$

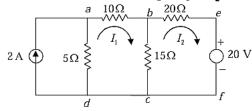

- **5.** Let I<sub>1</sub> and I<sub>2</sub> represent mesh currents in the loop abcda and befcb respectively. The correct expression describing Kirchoff's voltage loop law in one of the following loop is **[GATE 2008]**

- $(a)30I_1 15I_2 = 10$

- (b)  $-15I_1 + 20I_2 = -20$

- (c)  $30I_1 15I_2 = -10$

- (d)  $-15I_1 + 20I_2 = 20$

**6.** For a given load resistance  $R_L = 4.7$  ohm, the power transfer efficiencies  $\left(\eta = \frac{P_{load}}{P_{total}}\right)$  of a dc voltage source and a dc current source with internal resistances  $R_1$  and  $R_2$ , respectively, are equal. The product  $R_1R_2$  in units of ohm  $\frac{2}{2}$  (rounded off to one decimal place) is

[GATE 2019]

7. A power supply has internal resistance  $R_S$  and open load voltage  $V_S = 5$  V. When a load resistance  $R_L$  is connected to the power supply, a voltage drop of  $V_L = 4V$  is measured across the load. The value of  $\frac{R_L}{R_S}$  is (Round off to the nearest integer) [GATE 2022]

JEST PYQ

1. The ratio of maximum to minimum resistance that can be obtained with  $N1 - \Omega$  resistors is [JEST 2012]

(a) N

(b)  $N^2$

(c) 1

- (d) ∞

- 2. The temperature of a thin bulb filament (assuming that the resistance of the filament is nearly constant) of radius ' r' and length L is proportional to [JEST 2014]

(a)  $r^{1/4}L^{-1/2}$

(b)  $L^2r$

(c)  $r^{1/4}L^{-1}$

- (d)  $r^2 L^{-1}$

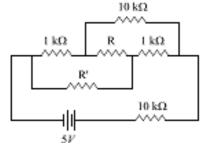

- 3. It is found that when the resistance R indicated in the figure below is changed from  $1k\Omega$  to  $10k\Omega$ , the current flowing through the resistance R' does not change. What is the value of the resistor R'?

[JEST 2016]

(a)  $5k\Omega$

- (b)  $100\Omega$

- (c)  $10k\Omega$

- (d)  $1K\omega$

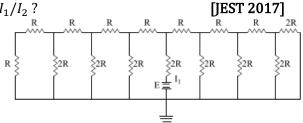

$\textbf{4.} \quad \text{For the circuit shown below, what is the ratio} \\$

Correct answer is (0016).

- 5. The ratio of maximum to minimum resistance that can be obtained with N number of  $3 \Omega$  resistors is [JEST 2020]

- (a) N

(b)  $N^2$

(c)  $N^{3}$

- (d)  $N^4$

- 6. A carbon rod of resistance  $R_c$  and a metal rod of resistance  $R_m$  are connected in series. Let their linear temperature coefficients of resistivity have magnitudes  $\alpha_c$  and  $\alpha_m$ , respectively. The condition that the net resistance would be independent of temperature is

[JEST 2020]

- (a)  $R_c = R_m$

- (b)  $\alpha_c = \alpha_m$

- $(c)\frac{R_c}{R_m} = \frac{\alpha_m}{\alpha_c}$

- (d)  $\frac{R_m}{R_c} = \frac{\alpha_m}{\alpha_c}$

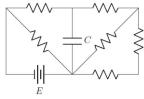

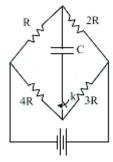

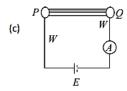

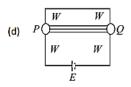

- 7. Consider the circuit shown in the figure below. *C* is the capacitance of the capacitor, *E* is the voltage provided by the battery and all the resistors are identical. What is the charge stored in the capacitor in units of *CE*, once it is fully charged. [JEST 2023]

(a)  $\frac{3}{4}$

(b)  $\frac{5}{8}$

(c)  $\frac{3}{6}$

- $(d)^{\frac{5}{4}}$

- 8. If a resistor of  $10k\Omega$  and a capacitor of  $0.5\mu$  F are connected in series across an AC supply of 220 V (rms) at 50 Hz , what is the average power (in mW , to the nearest integer) dissipated in the circuit? [JEST 2025]

# TIFR PYQ

1. In the circuit given below, a person measures 9.0 V across the battery, 3.0 V across the  $2M\Omega$  resistor  $R_A$  and 4.5 V across the unknown resistor  $R_B$ , using an ordinary voltmeter which has a finite input resistance r. Assuming that the battery has negligible internal resistance, it follows that (i) the resistance  $R_B$  and (ii) the input resistance r of the voltmeter are, in  $M\Omega$ ,

[TIFR 2009]

- $(a)R_B = 3.0, r = 6.0$

- (b)  $R_B = 2.5, r = 7.5$

- (c)  $R_B = 4.0, r = 12.0$

- (d)  $R_B = 4.5, r = 10.0$

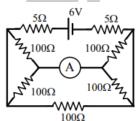

- 2. The current read by the ammeter (A) in the circuit given below is [TIFR 2011]

- (a) 27.3 Ma

- (b) 100.0 mA

- (c) 54.5 mA

- (d) 50.0 mA

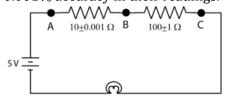

- 3. You are given the following circuit and two instruments: a voltmeter and an ammeter both with 0.001% accuracy in their readings.

Which of the following methods will result in the most accurate reading for the current without interrupting the current in the circuit?

[TIFR 2014]

(a) Use voltmeter to measure voltage across points B and C

- (b) Use the ammeter to measure current at point B

- (c) Use voltmeter to measure voltage across points A and B  $\square$

- (d) Use voltmeter to measure voltage across points A and C

- **4.** A student in the laboratory is provided with a bunch of standard resistors as well as the following instruments

- ----Voltmeter accurate to 0.1 V

- ---Thermometer accurate to 0.1C

- ----Ammeter accurate to 0.01 A

- ---Stop watch accurate to 0.05 s

- ----Constant current source (ideal)

- ---Constant voltage source (ideal)

Using this equipment (and nothing else), the student is expected to measure the resistance *R* of one of the given resistors. The least accurate result would be obtained by **[TIFR 2016]**

- (a) measuring the Joule heating.

- (b) passing a constant current and measuring the voltage across it.

- (c) measuring the current on application of a constant voltage across it.

- (d) the Wheatstone bridge method.

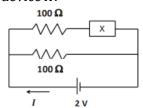

- **5.** The circuit shown below contains an unknown device *X*.

The current-voltage characteristics of the device X were determined and are shown in the plot given below. [TIFR 2016]

Determine the current I (in mA) flowing through the device X.

**6.** A realistic voltmeter can be modelled as an ideal voltmeter with an input resistor in parallel as shown below:

Such a realistic voltmeter, with input resistance  $1k\Omega$ , gives a reading of 100mV when connected to a voltage source with source resistance  $50\Omega$ . What will a similar voltmeter, with input resistance  $1M\Omega$ , read in mV, when connected to the same voltage source?] [TIFR 2018]

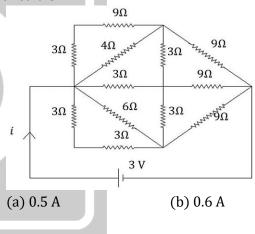

**7.** The current *i* flowing through the following circuit is

**8.** Consider the circuit shown on the right, which involves an op-amp and two resistors, with an input voltage marked INPUT.

Which of the following circuit components, when connected across the input terminals, is most likely to create a problem in the normal operation of the circuit? [TIFR 2018]

(d) 1.0 A

(c) 0.75 A

- (a) A voltage source with very high Thevenin resistance.

- (b) A current source with a very high Norton resistance.

- (c) A voltage source with a very low Thevenin resistance.

- (d) A current source with a very low Norton resistance.

- 9. A badly-designed voltmeter is modelled as an ideal voltmeter with a large resistor (R) and a large capacitor (C) connected in parallel to it. Given this information, which of the following statements describes what happens when this voltmeter is connected to a DC voltage source with voltage V and internal resistance  $r(r \ll R)$ ?

- (a) The reading on the voltmeter rises slowly and becomes steady at a value slightly less than *V*.

- (b) The reading on the voltmeter starts at a value slightly less than *V* and slowly falls to zero.

- (c) The reading on the voltmeter rises slowly to a maximum value close to *V* and then slowly goes to zero.

- (d) The reading on the voltmeter reads zero even when connected to the voltage source.

- 10. In an amplifier circuit, an input sine wave of amplitude 5 V gives a sine wave of amplitude 25 V as an output in an open load configuration. On applying a  $20k\Omega$  load resistance, the output drops to 10 V. This implies that the output resistance of the amplifier must be

[TIFR 2021]

- (a)  $2k\Omega$

- (b)  $20k\Omega$

- (c)  $10k\Omega$

- (d)  $30k\Omega$

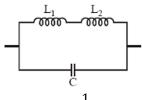

- **11.** It is required to design a circuit with an impedance  $Z(\omega)$  such that  $Z(\omega)=ik(\omega-\omega_0)$  for a range of frequencies  $\omega$  such that  $|\omega-\omega_0|/\omega_0\ll 1$  where k and  $\omega_0$  are constant real numbers.

A possible design for this circuit would correspond to

| ❖ Answer Key |          |    |   |  |    |      |    |      |     |     |

|--------------|----------|----|---|--|----|------|----|------|-----|-----|

| CSIR-NET     |          |    |   |  |    |      |    |      |     |     |

| 1.           | b/b      | 2. | С |  | 3. | b    | 4. | d    | 5.  | b   |

| 6.           | С        | 7. | b |  | 8. | a    | 9. | a    | 10. | b   |

| 11           | . b      |    |   |  |    |      |    |      |     |     |

| GATE         |          |    |   |  |    |      |    |      |     |     |

| 1.           | b        | 2. | a |  | 3. | a    | 4. | d    | 5.  | a   |

| 6.           | 22.09    | 7. | 4 |  |    |      |    |      |     |     |

|              | JEST PYQ |    |   |  |    |      |    |      |     |     |

| 1.           | b        | 2. | d |  | 3. | b    | 4. | 0016 | 5.  | b   |

| 6.           | С        | 7. | b |  | 8. | 3444 |    |      |     |     |

| TIFR PYQ     |          |    |   |  |    |      |    |      |     |     |

| 1.           |          | 2. |   |  | 3. | С    | 4. | a    | 5.  | 012 |

| 6.           | 105      | 7. | С |  | 8. | С    | 9. | a    | 10. | d   |

| 11           | . a      |    |   |  |    |      |    |      |     |     |

# **Diodes**

# **❖** CSIR-NET PYQ

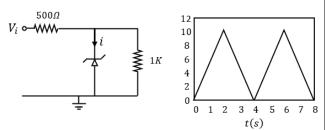

**1.** The figure below shows a voltage regulator utilizing a Zener diode of breakdown voltage 5 V and a positive triangular wave input of amplitude 10 V.

For  $V_i > 5$  V, the Zener regulates the output voltage by channeling the excess current through it self. Which of the following waveforms shows the current 'i' passing through the Zener diode? [CSIR-DEC 2011]

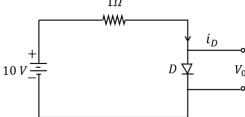

**2.** A diode D as shown in the circuit as an i - vrelation which can be proximated by

$$i_D = \begin{cases} v_D^2 + 2v_D, & \text{for } v_D > 0\\ 0, & \text{for } v_D \le 0 \end{cases}$$

The value of  $v_D$  in the circuit is:

# [CSIR-DEC 2012]

(a)

$$(-1 + \sqrt{11})V$$

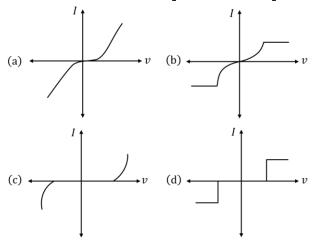

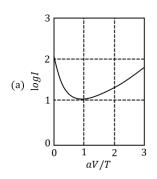

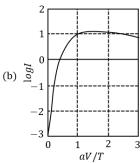

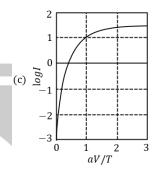

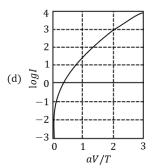

3. Two identical Zener diodes are placed back to back in series and are connected to a variable DC power supply. The best representation of the I-V characteristics of the circuit is

# [CSIR-DEC 2013]

**4.** The I - V characteristics of the diode in the circuit below is given by

$$I = \begin{cases} (V - 0.7)/500 & \text{for } V \ge 0.7\\ 0 & \text{for } V < 0.7 \end{cases}$$

where *V* is measured in volts and *I* is measured in amperes.

The current *I* in the circuit is

# [CSIR-DEC 2014]

(a) 10.0 mA

(b) 9.3 Ma

(c) 6.2 mA

(d)  $6.7 \, \text{mA}$

**5.** Let  $I_0$  be the saturation current,  $\eta$  the ideality factor and  $v_F$  and  $v_R$  the forward and reverse potentials, respectively, for a diode. The ratio  $R_R/R_F$  of its reverse and forward resistances  $R_R$ and  $R_F$  respectively, varies as (In the following  $k_B$  is the Boltzmani constant, T is the absolute temperature and q is the charge).

(a)

$$\frac{v_R}{v_F} \exp\left(\frac{qv_F}{\eta k_B T}\right)$$

(a)

$$\frac{v_R}{v_F} \exp\left(\frac{qv_F}{\eta k_B T}\right)$$

(b)  $\frac{v_F}{v_R} \exp\left(\frac{qv_F}{\eta k_B T}\right)$

$$(c)\frac{v_R}{v_F}\exp\left(-\frac{qv_F}{\eta k_B T}\right)$$

(c)

$$\frac{v_R}{v_F} \exp\left(-\frac{qv_F}{\eta k_B T}\right)$$

(d)  $\frac{v_F}{v_R} \exp\left(-\frac{qv_F}{\eta k_B T}\right)$

**6.** A Zener diode with an operating voltage of 10 V at 25°C has a positive temperature co-efficient of 0.07% per °C of the operating voltage. The operating voltage of this Zener diode at 125°C is

#### [CSIR-DEC 2017]

(a) 12.0 V

(b) 11.7 V

- (c) 10.7 V

- (d) 9.3 V

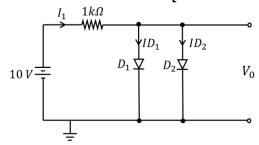

- 7. In the circuit below,  $D_1$  and  $D_2$  are two silicon diodes with the same characteristics. If the forward voltage drop of a silicon diode is 0.7 V, then the value of the current  $I_1 + I_D$ , is

## [CSIR-DEC 2017]

- (a) 18.6 mA

- (b) 9.3 mA

- (c) 13.95 mA

- (d) 14.65 Ma

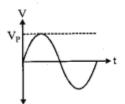

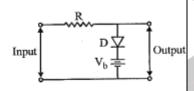

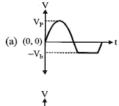

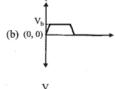

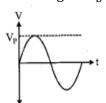

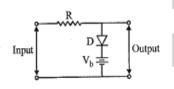

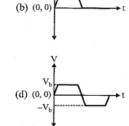

- **8.** A sinusoidal voltage having a peak value of  $V_P$  is an input to the following circuit, in which the DC voltage is  $V_b$ .

Assuming an ideal diode, which of the following best describes the output waveform?

# [CSIR-DEC 2018]

9. The forward diode current is given by  $I = \kappa T^{\alpha} e^{-E_{\mathbf{k}}/k_{p}T} (\exp{(\mathrm{eV}/k_{B}T)} - 1)$ , where  $E_{g}$  is the band gap of the semiconductor, V is the voltage drop across the diode, T is the temperature of the diode operating near room temperature and,  $\alpha$  and  $\kappa$  are constants. A diode is used as a thermal sensor in the circuit shown below.

If V is measured using an ideal voltmeter to estimate T, the variation of the voltage V as a function of T is best approximated by (in the following a and b are constants)

# [CSIR-JUNE 2019]

- (a)  $aT^2 + b$

- (b) aT + b

- (c)  $aT^3 + b$

- (d)  $aT + bT^2$

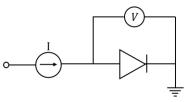

- **10.** In the circuit below, D is an ideal diode, the source voltage  $V_S = V_0 \sin \omega t$  is a unit amplitude sine wave and  $R_S = R_L$ .

[CSIR-DEC 2019]

The average output voltage  $V_L$ , across the load resistor  $R_L$  is

- (a)  $\frac{1}{2\pi}V_0$

- (b)  $\frac{3}{2\pi}V_0$

(c)  $3V_0$

- (d)  $V_0$

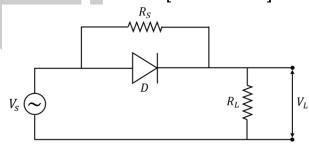

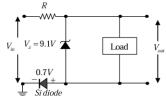

- **11.** A high impedance load network is connected in the circuit as shown below

The forward voltage drop for silicon diode is 0.7 V and the Zener voltage is 9.10 V. If the input voltage  $(V_{in})$  is sine wave with an amplitude of 15 V (as shown in the figure above), which of the following waveform qualitatively describes the output voltage ( $V_{out}$ ) across the load? [CSIR-JUNE 2022]

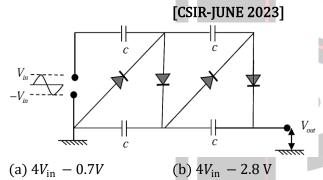

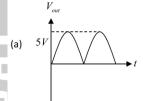

12. In the circuit shown below, four silicon diodes and four capacitors are connected to a sinusoidal voltage source of amplitude  $V_{\rm in} > 0.7$  V and frequency 1kHz. If the knee voltage for each of the diodes is 0.7 V and the resistances of the capacitors are negligible, the DC output voltage  $V_{\rm out}$  after 2 seconds of starting the voltage source is closest to

(c)

$$V_{\rm in} - 0.7 \text{ V}$$

(d)

$$V_{\rm in} - 2.8 \, \rm V$$

#### **❖** GATE PYQ

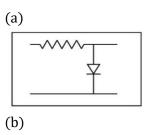

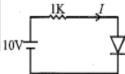

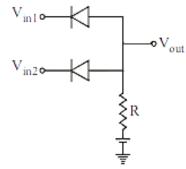

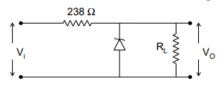

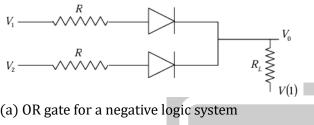

**1.** The circuit shown can be used as **[GATE 2005]**

- (a) NOR gate

- (b) OR gate

- (c) NAND gate

- (d) AND gate

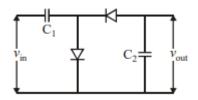

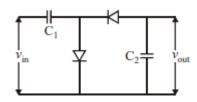

- **2.** A sinusoidal input voltage  $v_{\rm in}$  of frequency  $\omega$  is fed to the circuit shown in the figure, where  $C_1 \gg C_2$ . If  $v_m$  is the peak value of the input voltage, then output voltage  $(v_{\rm out})$  is

[GATE 2006]

(a)  $2v_m$

- (b)  $2v_0 \sin \omega t$

- (c)  $\sqrt{2}v_m$

- (d)  $\frac{v_m}{2} \sin \omega t$

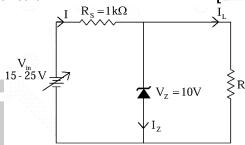

- **3.** Pick the correct statement based on the above circuit **[GATE 2009]**

- (a) The maximum Zener current,  $I_{z(max)}$  when  $R_L=10 {\rm k}\Omega$  is 15 mA

- (b) The minimum Zener current,  $I_{z(min)}$ , when  $R_L=10k\Omega$  is 5 mA

- (c) With  $V_{\rm in}=20$  V,  $I_L=I_Z$  when  $R_L=2k\Omega$

- (d) The power dissipated across the Zener when  $R_L=10 \mathrm{k}\Omega$  and  $V_{\mathrm{in}}=20~\mathrm{V}$  is  $100~\mathrm{mW}$

- **4.** In the following circuit, the voltage drop across the ideal diode in forward bias conditions is 0.7 V [GATE 2012]

The current passing through the diode is

- (a) 0.5 mA

- (b) 1.0 mA

- (c) 1.5 mA

- (d) 2.0 Ma

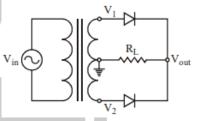

- **5.** In the figure given below, the input to the primary of the transformer is a voltage varying sinusoidally with time. The resistor *R* is

connected to the centre tap of the secondary. Which one of the following plots represents the voltage across the resistor R as a function of [GATE 2012] time?

- **6.** Consider the circuit given in the figure. Let the forward voltage drop across each diode be 0.7 V. The current I (in mA) through the resistor is [GATE 2020]

- 7. Choose the most appropriate matching of the items in Column 1 with those in Column 2. [GATE 2023]

| Column 1             | Column 2                                 |

|----------------------|------------------------------------------|

| (i) PIN diode        | P. Voltage regulation                    |

| (ii) Tunnel<br>diode | Q. Radio frequency and microwave devices |

| (iii) Zener<br>diode | R. Optoelectronic detection              |

| (iv) Photo<br>diode  | S. Oscillator                            |

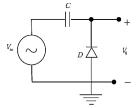

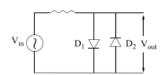

**8.** The symbols C, D,  $V_{\rm in}$  and  $V_0$  shown in the figure denote capacitor, ideal diode, input voltage and output voltage, respectively.

Which one of the following output waveforms  $(V_0)$  is correct for the given input waveform  $(V_{\rm in})$ ?

[GATE 2024]

# **❖** JEST PYQ

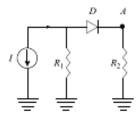

1. Consider the circuit shown in the figure where  $R_1 = 2.07 \text{k}\Omega$  and  $R_2 = 1.93 \text{k}\Omega$  current source Idelivers 10 mA current. The potential across the diode *D* is 0.7 V. What is the potential at *A*?

[JEST 2017]

(a) 10.35 V

(b) 9.65 V

(c) 19.30 V

(d) 4.83 V

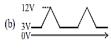

**2.** In the following silicon diode circuit ( $V_B$  = 0.7 V), determine the output waveform (  $V_{\rm out}$  ) for the given input wave. [JEST 2017]

3. A Germanium diode is operated at a temperature of 27 degree C. the diode terminal voltage is 0.3 V when the forward current is 10 mA. What is the forward current (in mA) if the terminal voltage is 0.4 V?

[JEST 2018]

- (a) 477.3

- (b) 577.3

- (c) 47.73

- (d) 57.73

- **4.** The circuit given below is fed by a sinusoidal voltage  $V_{\rm in} = V_0 \sin \omega t$ . Assume that the cut-in voltage of the diode is 0.7 volts and  $V_1$  is a positive dc voltage smaller than  $V_0$ . Which one of the following statements is true about  $V_{\rm out}$ ?

[JEST 2019]

- (a) Positive part of  $V_{\rm out}$  is restricted to a maximum voltage of 0.7  $+\frac{R_2}{R_1+R_2}V_1$

- (b) Negative part of  $V_{\rm out}$  is restricted to a maximum voltage of 0.7  $+\frac{R_2}{R_1+R_2}V_1$

- (c) Positive part of  $V_{\text{out}}$  is restricted to a maximum voltage of  $0.7 + \frac{R_1}{R_1 + R_2} V_1$

- (d) Negative part of  $V_{\text{out}}$  is restricted to a maximum voltage of  $0.7 + \frac{R_1}{R_1 + R_2} V_1$

- **5.** In an open circuited p-n junction diode, the barrier voltage at the junction is generated due to [JEST 2021]

- (a) Minority carriers in the p and n sides

- (b) Majority carriers in the p and n sides

- (c) Immobile negative charge in the p-side and positive charge in the n-side

- (d) Immobile positive charge in the *p*-side and negative charge in the *n*-side

- **6.** The circuit given in the figure below is composed of ideal diodes and resistances *R*. The input waveform is shown on the left.

The output waveform would be[JEST 2021]

7. What is the output waveform of the circuit for the given input signal? Assume that the zener diodes are identical, amplitude of the input voltage  $V_{\rm in}$  is twice the zener breakdown voltage, and  $R_L = 10R$ .

[JEST 2024]

Α.

В.

C.

D.

**8.** A silicon p-n junction diode operates at 27°C. The current *I* is doubled when the forward bias is increased. The increase in the forward bias is closest to:

[Assume  $I \gg I_s$ , where  $I_s$  is the reverse saturation current and the emission coefficient

$\eta_{\rm Si} = 2.$

[JEST 2025]

(a)54 mV

(b)36 mV

(c)72 mV

(d)18 mV

#### TIFR PYQ

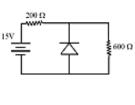

1. The voltage regulator circuit shown in the figure has been made with a Zener diode rated at 15 V, 200 mW. It is required that the circuit should dissipate 150 mW power across the fixed load resistor  $R_L$ . [TIFR 2012]

For stable operation of this circuit, the input voltage  $V_i$  must have a range

- (a) 17.5 V 20.5 V

- (b) 15.5 V 20.5 V

- (c) 15.5 V 22.5 V

- (d) 17.5 V 22.5 V

- (e) 15.0 V 22.5 V

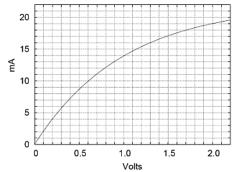

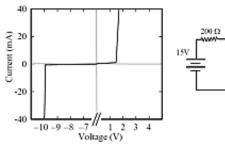

- 2. The figure on the right shows the current voltage characteristics of a diode over a range of voltage and current where it is safe to operate the diode. [TIFR 2013]

When this diode is used in the circuit on the extreme right, the approximate current, in mA, through the diode will be

(a) 0

- (b) 8.3

- (c) 16.7

- (d) 25

- **3.** Consider the following circuit.

Which of the graphs given below is a correct representation of  $V_{\text{out}}$ ? [TIFR 2014]

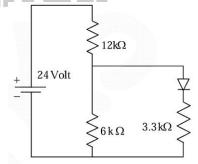

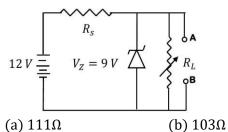

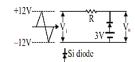

**4.** Drawing power from a 12 V car battery, a 9 V stabilized DC voltage is required to power a car stereo system, attached to the terminals *A* and *B*, as shown in the figure.

If a Zener diode with ratings,  $V_z = 9 \text{ V}$  and  $P_{\text{max}} = 0.27 \text{ W}$ , is connected as shown in the figure, for the above purpose, the minimum series resistance  $R_S$  must be **[TIFR 2019]**

- (c)  $100\Omega$

- (d)  $97\Omega$

- **5.** The signal shown on the left side of the figure below is fed into the circuit shown on the right side.

If the signal has time period  $\tau_S$  and the circuit has a natural frequency  $\tau_{RC}$ , then, in the case when  $\tau_S \ll \tau_{RC}$ , the steady-state output will resemble [TIFR 2019]

- (b)  $V_m$   $V_m$   $V_m$

- (c)  $-V_m$   $-2V_m$

- $(d) \quad V_{m}$

| ❖ Answer Key |       |      |      |       |  |  |

|--------------|-------|------|------|-------|--|--|

| CSIR-NET     |       |      |      |       |  |  |

| 1. a         | 2. d  | 3. c | 4. c | 5. b  |  |  |

| 6. c         | 7. c  | 8. c | 9. b | 10. a |  |  |

| 11. d        | 12. b |      |      |       |  |  |

| GATE         |       |      |      |       |  |  |

| 1. d         | 2. a  | 3. c | 4. b | 5. a  |  |  |

| 6. 8         | 7. a  | 8. 8 |      |       |  |  |

| JEST         |       |      |      |       |  |  |

| 1. b         | 2. b  | 3. a | 4. a | 5. c  |  |  |

| 6. a         | 7. a  | 8. b |      |       |  |  |

| TIFR PYQ     |       |      |      |       |  |  |

| 1. a         | 2. b  | 3. b | 4. c | 5. d  |  |  |

# **Bipolar Junction Transistor**

# **❖** CSIR-NET PYQ

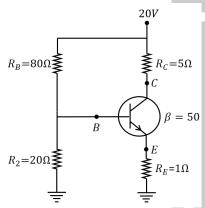

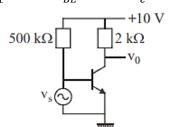

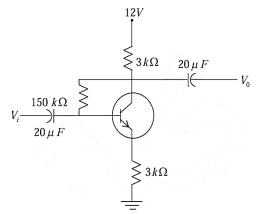

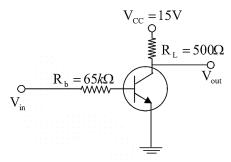

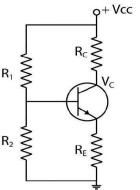

1. The transistor in the given circuit has  $h_{fc} = 35\Omega$ and  $h_{ie} = 1000\Omega$ . If the load resistance  $R_L =$  $1000\Omega$ , the voltage and current gain are, respectively. [CSIR-JUNE 2012]

- (a) -35, -35

- (b) 35, -35

- (c) 35, -0.97

- (d) 0.98, -35

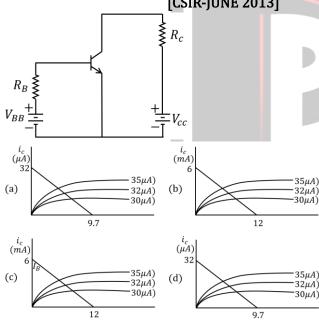

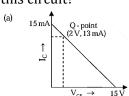

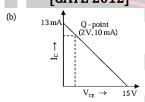

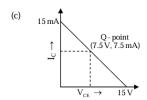

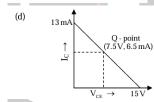

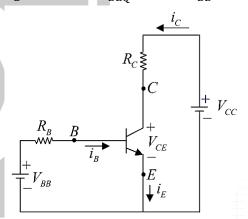

- A silicon transistor with built-in voltage 0.7 V is used in the circuit shown, with  $V_{BB} = 9.7 \text{ V}$ ,  $R_{B}$ =  $300 \text{k}\Omega$ ,  $V_{CC}$  = 12 V and  $R_{C}$  =  $2 \text{k}\Omega$ . Which of the following figures correctly represents the load line and the quiescent Q point?

[CSIR-JUNE 2013]

A large MOS transistor consists of N individual transistors connected in parallel. If the only form of noise in each transistor is 1/f noise, then the equivalent voltage noise spectral density for the MOS transistor is

[CSIR-DEC 2014]

- (a) 1/N times that of a single transistor

- (b)  $1/N^2$  times that of a single transistor

- (c) N times that of a single transistor

- (d)  $N^2$  times that of a single transistor

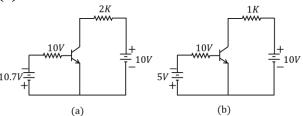

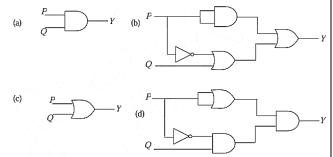

- **4.** Consider the circuits shown in Figures (a) and (b) below.

If the transistors in Figures (a) and (b) have current gain ( $\beta_{tik}$ ) of 100 and 10 respectively, then they operate in the [CSIR-JUNE 2015] (a) active region and saturation region respectively

- (b) saturation region and active region respectively

- (c) saturation region in both cases

- (d) active region in both cases

- 5. In the circuit below the voltages  $V_{BB}$  and  $V_{CC}$ are kept fixed, the voltage measured at B is a constant, but that measured at A fluctuates between a few  $\mu V$  to a few mV.

From these measurements it may be inferred [CSIR-DEC 2017] that the

- (a) base is open internally

- (b) emitter is open internally

- (c) collector resistor is open

- (d) base resistor is open

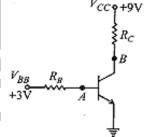

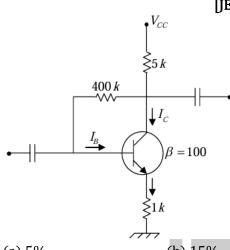

- In the following circuit, the value of the common-emitter forward current amplification factor  $\beta$  for the transistor is 100 and  $V_{BE}$  is 0.7 V.

The base current  $I_B$  is

[CSIR-JUNE 2018]

- (a)  $40 \mu A$

- (b)  $30\mu A$

- (c) 44µA

- (d) 33μA

- **7.** An *npn*-transistor is connected in a voltage divider configuration as shown in the figure below

If the resistor  $R_2$  is disconneted, the voltages  $V_B$  at the base and  $V_c$  at the collector change as follows. **[CSIR-JUNE 2019]**

- (a) Both  $V_{\rm B}$  and  $V_{\rm C}$  increase

- (b) Both  $V_{\rm B}$  and  $V_{\rm C}$  decrease

- (c)  $V_B$  decreases, but  $V_C$  increase

- (d)  $V_B$  increases, but  $V_C$  decreases

- **8.** In a collector feedback circuit shown in the figure below, the base emitter voltage  $V_{BE} = 0.7 \text{ V}$  and current gain  $\beta = \frac{I_C}{I_B} = 100$  for the transistor

The value of the base current  $I_B$  is

[CSIR-DEC 2019]

- (a)  $20\mu A$

- (b)  $40 \mu A$

- (c)  $10\mu A$

- (d)  $100 \mu A$

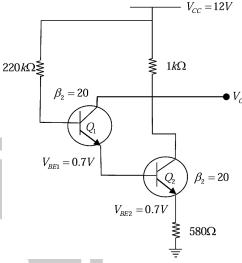

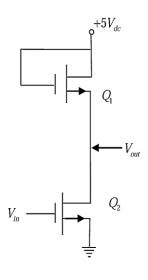

- 9. The figure below shows a circuit with two transistors,  $Q_1$  and  $Q_2$ , having current gains  $\beta_1$  and  $\beta_2$  respectively.

The collector voltage V<sub>C</sub> will be closest to

[CSIR-JUNE 2022]

- (a)0.9 V

- (b)2.2 V

- (c)2.9 V

- (d)4.2 V

- 10. An amplifier with a voltage gain of 40 dB without feedback is used in an electronic circuit. A negative feedback with a fraction 1/40 is connected to the input of this amplifier. The net gain of the amplifier in the circuit is closest to

[CSIR-JUNE 2022]

- (a)40 dB

- (b)37 dB

- (c)29 dB

- (d)20 Db

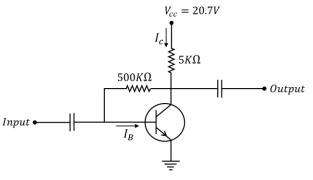

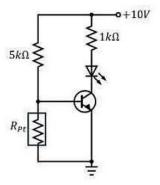

- 11. An LED is required to glow brightly when the temperature sensed by a Platinum resistance thermometer exceeds a certain value. In the circuit shown below, the resistance of the Pt thermometer (in ohms) varies as

$$R_{Pt}(T) = 100 + 0.4 T$$

where T is temperature in degree Celsius. The transistor turns on when  $V_{BE} > 0.7$  V and it has a very high current gain. The temperature at which the LED would start glowing is closest to

[CSIR DEC 2024]

(a)850°C

(b)400°C

(c)500°C

(d)700°C

# **❖** GATE PYQ

- **1.** In an n p n transistor, the leakage current [GATE 2001]

- (a) electrons moving from the base to the emitter

- (b) electrons moving from the collector to the base

- (c) electrons moving from the collector to the emitter

- (d) electrons moving from the base to the collector

- **2.** A bipolar junction transistor with one junction forward biased and either the collector or emitter open, operates in the [GATE 2004] (a) cut-offregion (b) saturation region

- (c) pinch-offregion

- (d) active region

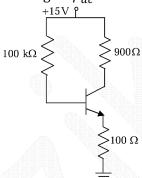

- **3.** Figure shows a common emitter amplifier with  $\beta = 100$ . What is the maximum peak to peak input signal  $(v_s)$  for which is distortion-free output may be obtained? [GATE 2004] [Assume  $V_{BE} = 0$  and  $r_e = 20\Omega$ ]

- (a) 40mV

- (b) 60Mv

- (c) 80mV

- (d) 100mV

**4.** Calculate the collector voltage  $(v_c)$  of the transistor circuit is shown in the figure. [Given:  $\alpha=0.96$ ,  $I_{CB0}=20\mu\mathrm{A}$ ,  $V_{BE}=$ 0.3 V,  $R_B = 100 \text{k}\Omega$ ,  $V_{CC} = +10 \text{ V}$  and  $R_C =$  $2.2k\Omega$ [GATE 2004]

- (a) 3.78 V

- (b) 3.82 V

- (c) 4.72 V

- (d) 9.7 V

- **5.** A power amplifier gives 150 W output for an input of 1.5 W. The gain, in dB, is **[GATE 2007]**

- (a) 10

(b) 20

(c) 54

- (d) 100

- **6.** In a typical *npn* transistor the doping concentrations in emitter, base and collector regions are C<sub>E</sub>, C<sub>B</sub> and C<sub>C</sub> respectively. These satisfy the relation [GATE 2007]

- (a)  $C_E > C_C > C_B$  (b)  $C_E > C_B > C_C$

- (c)  $C_C > C_B > C_E$  (d)  $C_E = C_C > C_B$

- **7.** A common emitter transistor amplifier circuit is operated under a fixed bias. In this circuit, the operating point [GATE 2008]

- (a) remains fixed with an increase in temperature

- (b) moves towards cut-off region with an increase in temperature

- (c) moves towards the saturation region with a decrease in temperature

- (d) moves towards the saturation region with an increase in temperature

- **8.** An amplifier of gain 1000 is made into a feedback amplifier by feeding 9.9% of its output voltage in series with the input opposing. If  $f_L =$ 20 Hz and  $f_H = 200$ kHz for the amplifier without feedback, then due to the feedback

[GATE 2009]

(a) the gain decreases by 10 times

- (b) the output resistance increases by 10 times

- (c) the  $f_H$  increases by 100 times

- (d) the input resistance decreases by 100 times

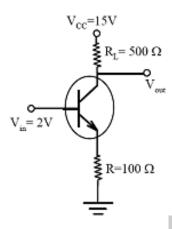

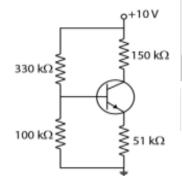

- 9. Consider the following circuit in which the current gain  $\beta_{dc}$  lof the transistor is 100

Which one of the following correctly represent the load line (collector current  $I_C$  with respect to collector emitter voltage  $V_{CE}$ ) and Q-point of this circuit? [GATE 2012]

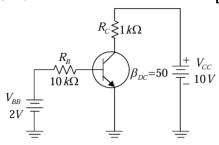

10. The current gain of the transistor in the following circuit is  $\beta_{dc}=100$ . The value of collector current  $I_C$  is **[GATE 2014]**

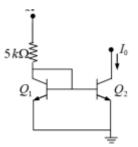

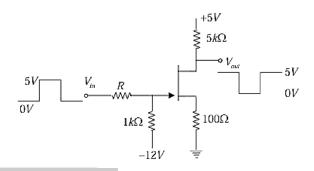

**11.** In the simple current source shown in the figure,  $Q_1$  and  $Q_2$  are identical transistors with current gain  $\beta=100$  and  $V_{BE}=0.7$  V

The current  $I_0$  (in mA)\_\_\_\_\_ is ( upto two decimal places) [GATE 2015]

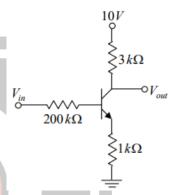

**12.** For the transistor shown in the figure, assume  $V_{BE} = 0.7 \text{ V}$  and  $\beta_{dc} = 100$ . If  $V_{\text{in}} = 5 \text{ V}$ ,  $V_{\text{out}}$  (in Volts) is\_\_\_\_\_ (Give your answer upto one decimal place) [GATE 2016]

13. For the transistor amplifier circuit shown below with  $R_1=10k\Omega$ ,  $R_2=10k\Omega$ ,  $R_3=1k\Omega$  and  $\beta=99$ . Neglecting the emitter diode resistance, the input impedance of the amplifier looking into the base for small ac signal is  $k\Omega$ . (up to two decimal places)

[GATE 2017]

14. For a bipolar junction transistor, which of the following statements are true? [GATE 2022](a) Doping concentration of emitter region is more than that in collector and base region

- (b) Only electrons participate in current conduction

- (c) The current gain  $\beta$  depends on temperature

- (d) Collector current is less than the emitter current

- **15.** For a transistor amplifier, the frequency response is such that the mid band voltage gain is 200. The cutoff frequencies are 20 Hz and 20kHz. What is the ratio (rounded off to two decimal places) of the voltage gain at 10 Hz to that at 100kHz? **[GATE 2023]**

- **16.** A typical biasing of a silicon transistor is shown in figure.

The value of common-emitter current gain  $\beta$  for the transistor is 100 . Ignore reverse saturation current. The output voltage  $V_0$  (in V ) is (in integer). [GATE 2024]

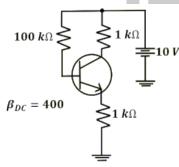

17. In the transistor circuit shown in the figure,  $V_{BE}=0.7 \text{ V}$  and  $\beta_{DC}=400$ . The value of the base current in  $\mu\text{A}$  (rounded off to one decimal place) is

# **❖** JEST PYQ

1. A transistor in common base configuration has ratio of collector current to emitter current  $\beta$  and ratio of Collector to base current  $\alpha$ . Which of the following is true? [JEST 2016]

$$(a)\beta = \frac{\alpha}{(\alpha+1)}$$

(b)

$$\beta = \frac{(\alpha + 1)}{\alpha}$$

$$(c)\beta = \frac{\alpha}{(\alpha - 1)}$$

(d)

$$\beta = \frac{(\alpha - 1)}{\alpha}$$

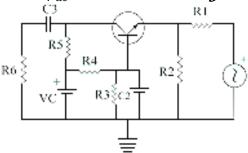

2. What is the DC base current (approximated to nearest integer value in  $\mu$ A ) for the following n-p-n silicon transistor circuit, given  $R_1=75\Omega$ ,  $R_2=4.0\mathrm{k}\Omega$ ,  $R_3=2.1\mathrm{k}\Omega$ ,  $R_4=2.6\mathrm{k}\Omega$ ,  $R_5=6.0\mathrm{k}\Omega$ ,  $R_6=6.8\mathrm{k}\Omega$ ,  $C_1=1\mu F$ ,  $C_2=2\mu F$ ,  $V_C=15V$  and  $\beta_{dc}=75$ ? [JEST 2017]

(a) 20

(b) 24

(c) 16

- (d) 35

- 3. Consider the transistor circuit shown in the figure. Assume  $V_{BEO} = 0.7 \text{ V}$ ,  $V_{BB} = 6 \text{ V}$

And the leakage current is negligible. What is the required value of  $R_B$  in kilo-ohms if the base current is to be  $4\mu A$ ?

[JEST 2018]

**4.** Calculate the collector current and determine whether or not the transistor in figure shown below is in saturation. Assume  $V_{CE}(\text{ sat }) = 0.2 \text{ V}$  [JEST 2020]

- (a) 6.5 mA, not in saturation

- (b) 11.5 mA, in saturation

- (c) 11.5 mA, not in saturation

- (d) 6.5 mA, in saturation

- 5. Analyze the common emitter transistor circuit given in the figure. If the current gain  $(\beta)$  increases by 50%, the relative change in collector current  $(I_C)$  is approximately

[JEST 2020]

(a) 5%

(b) 15%

- (c) 20%

- (d) 25%

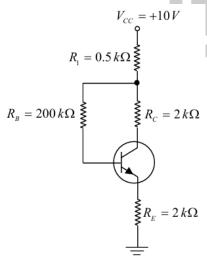

- 6. In the following transistor circuit  $R_1 = 0.5 \text{k}\Omega$ ,  $R_E = R_C = 2 \text{k}\Omega$ ,  $R_B = 200 \text{k}\Omega$ ,  $\beta = \frac{l_C}{l_B} = 100$ ,  $V_{CC} = 10 \text{ V}$ ,  $V_{BE} = 0.7 \text{ V}$ . Determine the  $V_{CE}$  in mV. [JEST 2021]

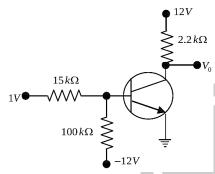

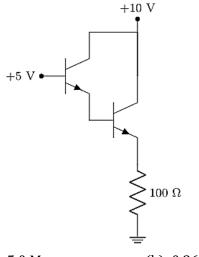

7. The base current in the first transistor of the following circuit having two identical Siliconbased npn transistors of  $\beta$  value 100, is closest to [JEST 2022]

- (a) 5.0 Ma

- (b) 0.36 mA

- (c)  $3.6\mu A$

- (d) 5.0μA

### TIFR PYQ

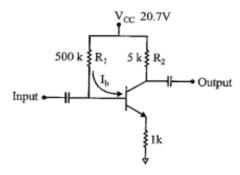

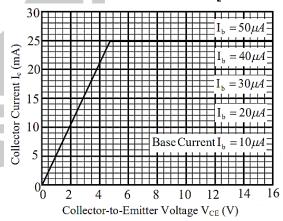

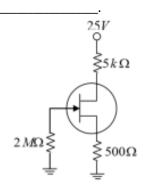

**1.** A plot of the common-emitter characteristics of a silicon n-p-n transistor is shown below. Given this information, and assuming that there will be a 0.7 V drop across a forward biased silicon p-n junction, the approximate value of the output voltage  $V_{\text{out}}$  for an input voltage  $V_{\text{in}} = 2 \text{ V}$  in the adjacent circuit will be

[TIFR 2009]

(a) 4 V

(b) 6 V

(c) 8 V

- (d) 10 V

- (e) 12 V

- (f) 14 V

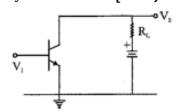

**2.** The circuit depicted on the right has been made with a silicon n-p-n transistor.

Assuming that there will be a 0.7 V drop across a forward-biased silicon p-n junction, the power dissipated across the transistor will be,

approximately,

[TIFR 2013]

- (a) 53 mW

- (b) 94 mW

- (c) 17 mW

- (d) 67 Mw

- **3.** All resistors in the circuit on the right have a tolerance of  $\pm 5\%$ .

Assuming a diode drop of 0.7 V, which of the following is the lowest possible value of the collector voltage? [TIFR 2014]

- (a) 3.1 V

- (b) 4.1 V

- (c) 4.7 V

- (d) 5.2 V

- **4.** In the transistor circuit shown on the right, assume that the voltage drop between the base and the emitter is 0.5 V.

What will be the ratio of the resistances  $R_2/R_1$ , in order to make this circuit function as a source of constant current, l = 1mA?

[TIFR 2016]

(a) 4.5

(b) 3.0

(c) 2.5

- (d) 2.0

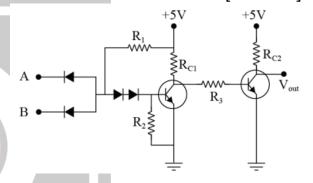

- **5.** Which digital logic gate is mimicked by the following silicon diode and silicon transistor circuit? [TIFR 2017]

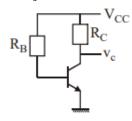

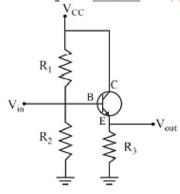

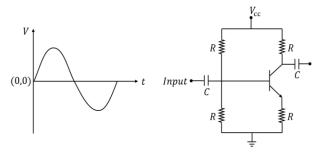

The circuit shown below represents a typical voltage-divider bias circuit for a transistor. Assume that resistance values and voltage values are typical for using the transistor as an amplifier. [TIFR 2020]

Which of the following changes in the circuit would result in an increase in the collector voltage  $V_C$ ?

- (a) R<sub>2</sub> is decreased slightly

- (b)  $R_2$  is increased slightly

- (c) R<sub>c</sub> is decreased slightly

# (d) $R_c$ is increased slightly

| ❖ Answer Key |            |           |         |       |  |  |  |  |  |

|--------------|------------|-----------|---------|-------|--|--|--|--|--|

|              | CSIR-NET   |           |         |       |  |  |  |  |  |

| 1. a         | 2. c       | 3. a      | 4. b    | 5. d  |  |  |  |  |  |

| 6. d         | 7. d       | 8. a      | 9. b    | 10. c |  |  |  |  |  |

| 11. d        |            |           |         |       |  |  |  |  |  |

|              |            | GATE      |         |       |  |  |  |  |  |

| 1. c         | 2. c       | 3. d      | 4. a    | 5.    |  |  |  |  |  |

| 6. a         | 7. a       | 8. c      | 9. a    | 10.   |  |  |  |  |  |

| 11. 5.6to5.9 | 12. 5.7    | 13. 5     | 14. acd | 15.   |  |  |  |  |  |

| 16. 12       | 17. 18.6μΑ |           |         |       |  |  |  |  |  |

|              |            | JEST      |         |       |  |  |  |  |  |

| 1. a         | 2. a       | 3. 1325Κω | 4. a    | 5. b  |  |  |  |  |  |

| 6. 0950      | 7. c       |           |         |       |  |  |  |  |  |

|              |            | TIFR      |         |       |  |  |  |  |  |

| 1.           | 2. b       | 3. b      | 4. d    | 5.    |  |  |  |  |  |

| 6. a         |            |           |         |       |  |  |  |  |  |

GATE Q.15: 2.20 to 2.36

TIFR Q. 5: AND or (A.B)

# MOSFET, JFET

# **❖** CSIR-NET PYQ

1. Consider an n-MOSFET with the following parameters: current drive strength  $K = 60\mu\text{A}/\text{V}^2$ , breakdown voltage  $BV_{DS} = 10 \text{ V}$ , ratio of effective gate width to the channel length  $\frac{W}{L} = 5$  and threshold voltage  $V_{\text{th}} = 0.5 \text{ V}$ . In the circuit given below, this n-MOSFET is operating in the [CSIR-DEC 2015]

- (a) ohmic region

- (b) cut-off region

- (c) saturation region

- (d) breakdown region

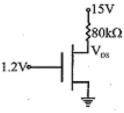

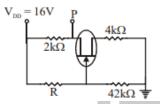

- 2. In the *n*-channel JFET shown in figure below,  $V_i = -2 \text{ V}$ , C = 10 pF,  $V_{DD} = +16 \text{ V}$  and  $R_D = 2 \text{k}\Omega$ .

If the drain D-source S saturation current  $I_{DSS}$  is 10 mA and the pinch-off voltage  $V_P$  is -8 V, then the voltage across points D and S is

[CSIR-JUNE 2017]

- (a) 11.125 V

- (b) 10.375 V

- (c) 5.75 V

- (d) 4.75 V

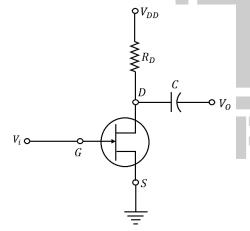

- **3.** The circuit containing two n-channel MOSFETs shown below, works as **[CSIR-JUNE 2022]**

- (a)a buffer

- (b)an inverter

- (c)a non-inverting amplifier

- (d)a rectifier

### GATE PYQ

- 1. An *n*-channel silicon (dielectric constant = 12) FET with a channel width  $a = 2 \times 10^{-6}$  m is doped with  $10^{21}$  electrons /m<sup>3</sup>. The pinch-off voltage is [GATE 2001]

- (a) 0.86 V

- (b) 0.68 V

- (c) 8.6 V

- (d) 6.8 V

- 2. The pinch-down voltage of a p-channel junction FET is  $V_P = 5$  V and the drain-to-source saturation current  $I_{DSS} = -40$  mA. The value of drain-source voltage  $V_{DS}$  is such that the transistor is operating in the saturated region. The drain current is given as  $I_D = -15$  mA. Find the gate-source voltage  $V_{GS}$ . [GATE 2001]

- **3.** A field effect transistor is a **[GATE 2004]** (a)unipolar device

- (b) special type of biopolar junction transistor

- (c) unijunction device

- (d) device with low input impedance

- **4.** A junction field effect transistor behaves as a **[GATE 2005]**

- (a) voltage controlled current source

- (b) voltage controlled voltage source

- (c) current controlled voltage source

- (d) current controlled current source

- 5. In the circuit shown, the voltage at test point P is 12 V and the voltage between gate and source is -2 V. The value of R (in  $k\Omega$ ) is

[GATE 2007]

(a) 42

(b) 48

(c) 56

(d)70

6. Under normal operating conditions, the gate terminal of an n-channel junction field effect transition (JFET) and an n-channel metal oxide semiconductor field effect transistor (MOSFET) are

[GATE 2008]

- (a) both biased with positive potentials

- (b) both biased with negative potentials

- (c) biased with positive and negative potentials respectively

- (d) biased with negative and positive potentials respectively

- 7. In the given circuit, the voltage across the source resistor is 1V. The drain voltage (in V) is—\_\_\_\_\_. [GATE 2015]

**8.** An n - channel FET having Gate-Source switch-off voltage  $V_{GS(OFF)} = -2V$  is used to invert a 0-5 V square-wave signal as shown. The maximum allowed value of R would be **[GATE 2018]**

(up to two decimal places).

|    | ❖ Answer Key |    |    |    |   |    |   |    |   |

|----|--------------|----|----|----|---|----|---|----|---|

|    | CSIR-NET     |    |    |    |   |    |   |    |   |

| 1. | d            | 2. | d  | 3. | b |    |   |    |   |

|    | GATE         |    |    |    |   |    |   |    |   |

| 1. | a            | 2. | a  | 3. | a | 4. | a | 5. | d |

| 6. | b            | 7. | 15 | 8. |   |    |   |    |   |

Ans: GATE Q.8:  $0.70 k\Omega$

# Semiconductor

# **❖** CSIR-NET PYQ

- 1. Light of wavelength 660 nm and power of 1 mW is incident on a semiconductor photodiode with an absorbing layer of thickness of (ln 4) $\mu$ m.

- (A) If the absorption coefficient at this wavelength is  $10^4$  cm<sup>-1</sup> and if 1% power is lost on reflection at the surface, the power absorbed will be [CSIR JUNE 2011]

- (a) 750μW

- (b) 675μW

- (c)  $250 \mu W$

- (d) 225μW

- (B) The generated photo-current for a quantum efficiency of unity will be

- (a)  $360 \mu A$

- (b) 400μA

- (c)  $133\mu A$

- (d) 120µA

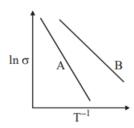

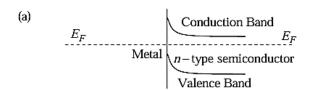

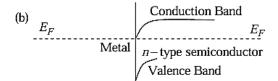

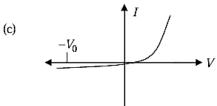

- **2.** A junction is made between a metal of work function  $W_M$ , and a doped semiconductor of work function  $W_S$  with  $W_M > W_S$ . If the electric field at the interface has to be increased by a factor of 3, then the dopant concentration in the semiconductor would have to be

[CSIR-DEC 2014]

- (a) increased by a factor of 9

- (b) decreased by a factor of 3

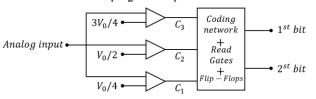

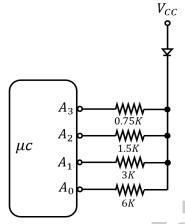

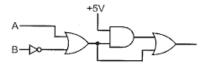

- (c) increased by a factor of 3